Profile - CN008

CN008

基于实时图像识别技术的视频游戏平台

清华大学微纳电子系

Project

Name of Project: 基于实时图像识别技术的视频游戏平台

Contact Information

Name: 谭波 E-Mail: aaatanbo@gmail.com Telephone: 01051776127 Mobile Phone: 15110079656 Mailing Address: 北京市海淀区清华大学FIT大楼4-508

Contest Advisor

Name: 张春 E-Mail: zhangchun@tsinghua.edu.cn Telephone: 62792912

Members

No. Name English Name 1 谭波 aaatanbo@gmail.com tanbo 2 刘继尧 flow002@sina.com liujiyao 3 阳祥秋 passionyg@163.com yangxiangqiu

Project Paper - view as Preliminary(2010/06/01), Final(2010/09/18), Draft, Latest

1. 设计概述 (Preliminary Paper)

设计意图:智能人机交互是一个应用广泛的技术,将智能人机交互技术应用到游戏操作等领域,无疑会大大的提高游戏的娱乐性、互动性。基于图像识别的游戏输入是利用图像识别的原理;识别人体的各个部位,根据对各个部位的运动分析,通过DE2-70开发板上的GPIO接驳外部一个硬件模拟USB键盘操作来实现对游戏等软件的控制。本设计不用外部标记,利用人体本身的特征,实现较智能化的人机交互,使游戏者从键盘鼠标中解放出来,提升游戏的娱乐性。各个部位的运动的意义可以自定义,可以实现多种游戏及其他软件的控制,具有较好的兼容性。适用范围:模拟USB键盘输入,以实现与游戏等软件的接驳,无需特定的驱动,在Windows XP及以后的系统上能够直接使用,适用于只需要键盘就能完全控制的游戏或者其他的软件。后期再开发一些PC机接驳程序,能实现部分鼠标的功能,可扩展性很强。选用cyclone系列器件的原因:本设计需要实时处理大量图像数据,并且需要较小的延时,实时性要求很高。所以将大部分数据处理以及操作使用硬件加速,所以选用FPGA来完成本设计。在设计中采用两个CPU协同处理,由于CPU和硬件之间有大量和频繁的数据交互,所以将CPU内置于FPGA内部,在本设计中我们选用两个NIOS II软核, NIOS II具有良好的可扩展性以及定制硬件IP和定制指令等功能在大大的提高了数据处理效率的同时也节约了设计者的时间。我们选用ALTERA DE2-70开发板作为开发平台,该开发板的核心是cyclone II EP2C70,具有高达70000个逻辑单元,而且价格低廉,是消费类数码产品开发的首选. DE2-70拥有很丰富的存储器,以及多媒体外设,在本设计中用到了视频A/D,两块SDRAM,一块SRAM等.DE2-70还提供了很多的开发范例,为项目的进度节约了大量的时间。

(Revision: 3 / 2010-08-28 09:15:11)

2. 功能描述 (Final Project Paper)

本设计是利用摄像头捕获操作者的行为,然后经过分析计算,得到操作者的意图,然后通过键盘模块发送控制命令到PC。本设计使用DE2-70上一个视频A/D将一个普通摄像头的数据采集到FPGA中,在FPGA内部通过解码,裁剪,数据重组,格式转换等方法获得需要640×480大小的数据。由于原始图像存在较多噪点及干扰,使用滤波模块将图像数据滤波,得到较干净的图像数据。所得到的数据将被分成三路,一路送到一个SDRAM存储器用以完成帧减的;另外一路送到VGA做调试显示;第三路被压缩后送到一个CPU外部硬件模块上,该模块由5块双口RAM组成,这是由于压缩后的图像数据不是2的N次方,所以为了节约片内存储器,则使用5块小的RAM内拼成一个大的存储器。第一路数据,在SDRAM中缓存了8帧,将当前数据和前N(7>N>4)进行帧减,然后通过腐蚀和膨胀算法去掉噪点和填充内部缺失,在这个过程中要实现帧减后的二值图像的压缩。用一个八面体去提取运动边界,然后提取出特征点坐标,并将坐标发送到主CPU的外挂模块上。第二路数据,作为调试数据,将会通过7个模块,6个叠加框模块,以及1个二值图像叠加模块,这7个模块均挂在主CPU上,由CPU根据需要叠加相应内容,实现算法和人的交互。第三路数据,这一路数据之所以要映射到片内,主要是为了主CPU快速的读取数据。以便主CPU能够直接的访问到图像数据。主CPU通过帧减以及全屏搜索等多种方法确定特征点(手、头、脚)的位置,然后通过硬件搜索模块在内存(SDRAM)中跟踪搜索特征点,并返回特征点的实时特征(由于光线的变化,可能导致特征区域特征值的变化,所以采用动态更新特征的方法)。主CPU在确定了头、手、脚等部位的坐标后,将这些坐标通过一个硬件模块CPU_BRIDGE发送到辅助CPU。辅CPU 根据当前寄存器中的值,控制外部硬件设备向PC发送控制命令,外部硬件设备将向PC发送相应的键盘操作。(Revision: 3 / 2010-08-28 09:16:16)

3. 性能参数 (Final Project Paper)

本设计要求系统能达到每秒实时处理60帧640×480的图像的能力,为了达到操作游戏的目的,要求操作延时较小。1、图像处理能力分析本设计采用的摄像头为25帧/s,分为奇偶场输出,为了调试需要,在缓存调整完图像数据以后,图像的数据帧率变为60帧/s,为了达到实时处理,CPU不直接处理大量的图像数据流,只是对少量图像数据采样。这样便能达到实时处理60帧/s的图像数据流。2、延时分析本设计采用的摄像头的数据并不是规则的数据流,需要先将数据缓存在SDRAM中,对图像的大小以及奇偶场进行调整,为了防止读写同一帧,缓存数据总共4帧,读出数据最大滞后将有2/60秒。硬件帧减部分总共缓存8帧数据,最大可造成延时有4/60秒。这样,系统的主要延时为1/10秒,其余的延时包括摄像头采集数据的延时以及发送命令到PC的延时。从最终的测试结果来看,对于操纵赛车游戏能达到很好的效果,这表明从操作者发出动作到PC接收到命令的延时在一个比较理想的值。3、硬件系统支持为了达到上述目的,我们大量使用了硬件加速,Altera的Nios II的定制IP功能,方便的将硬件加速模块快速的接驳到CPU,这样方便数据的交换,降低了开发的难度。很好的保证系统的复杂控制和大量计算的需要。(Draft / 2010-08-28 09:19:30)

4. 设计结构 (Preliminary Paper)

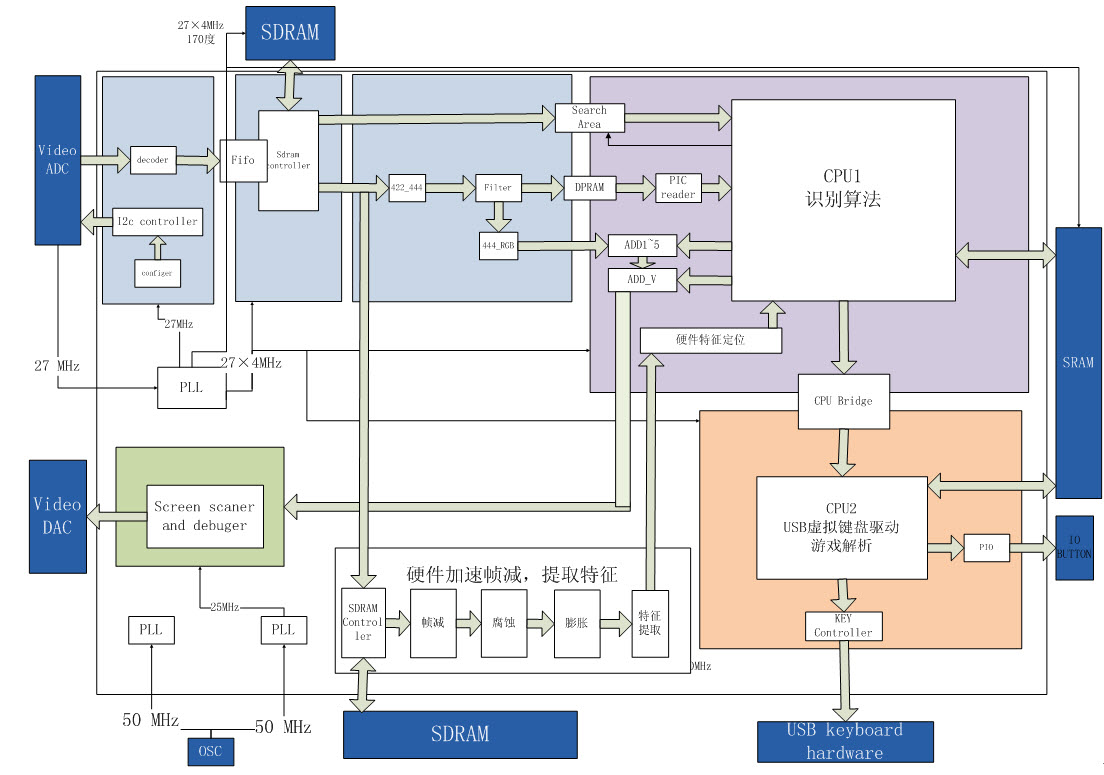

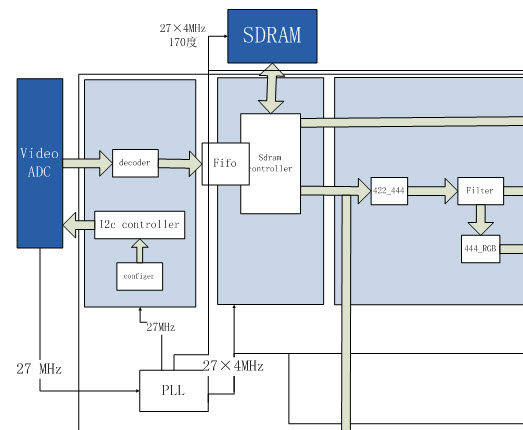

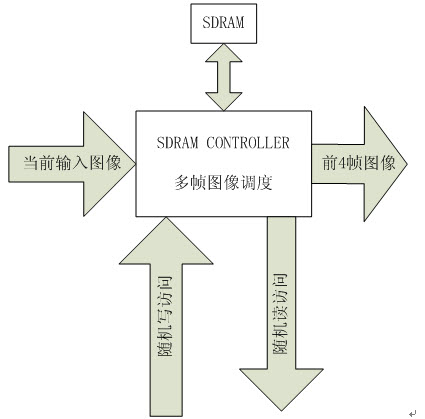

视频游戏控制平台结构图示意图如下:

系统硬件组成可以划分为图像获取与视频解码、图像识别、USB虚拟键盘控制及调试与监视模块四个主要组成部分。摄像头获取的视频数据暂存在SDRAM中,便于数据率的调整和图像大小的调整。一方面视频数据经过图像获取与视频解码模块后变为标准YUV444数据流,作为图像识别算法的数据源,并经过YUV2RGB模块后变为标准RGB数据流供调试与监视模块产生VGA扫频信号数据源。图像识别部分由图像获取与视频解码模块处取得图像数据,提取人的双手双脚等特征点并跟踪其运动,特征点的标注于运动跟踪信息传送给调试与监视模块,并将跟踪到的人的运动信息发送给USB虚拟键盘控制模块。虚拟键盘控制模块根据所获得的运动信息将人的运动解析为键盘命令并通过USB接口发送给PC机,完成游戏控制。

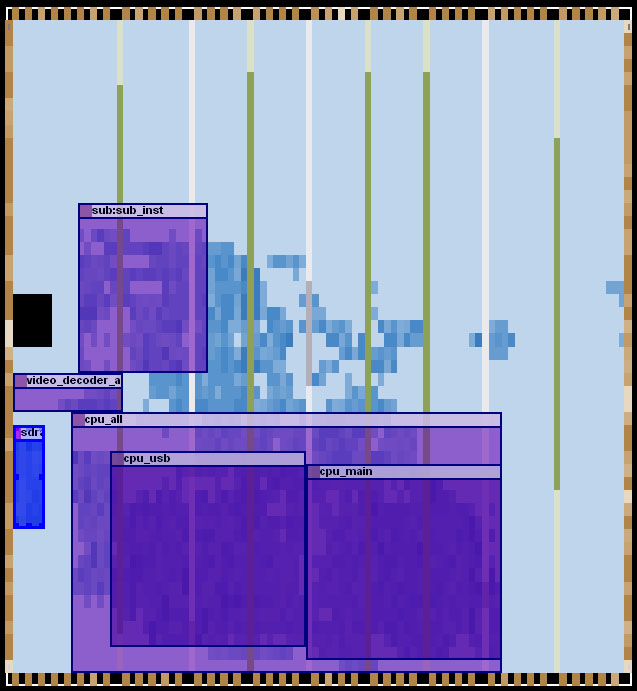

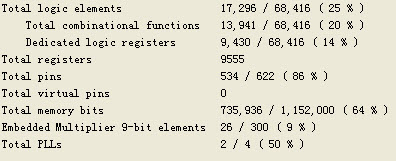

本设计使用EP2C70F896C6, 资源占用情况如下图所示:

1. 图像获取与视频解码单元

图像获取及预处理单元

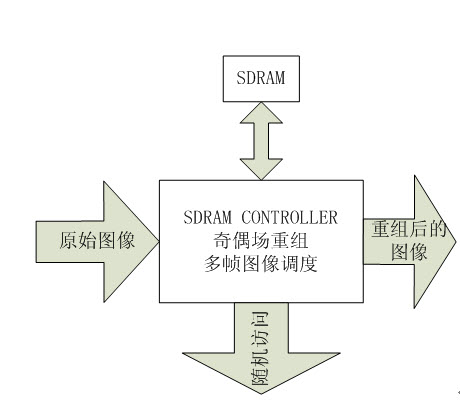

摄像头所捕捉到的数据为模拟电视色差信号,经过DE2电视解码芯片ADV7180处理后变为YUV422格式数据。由硬件控制器完成对ADV7180的控制及输出信号的调理后,将所获得的数据由SDRAM控制器存储于SDRAM中。SDRAM控制器除了提供一个写端口以供解码器存储视频数据外,还提供两个读端口,一个读端口供图像识别处理器系统所用,使其能够灵活的访问完整的视频数据帧,为识别算法的设计提供最大的灵活性,另一个读端口基于VGA的扫屏监视模块提供原始数据。SDRAM控制器各端口的优先级以及控制器的读写效率都经过仔细的设计,保证系统数据流的安全。原始图像的边缘质量不是很好,截取其中心部分,图像获取单元提供656*482格式的数据帧。为了保证读出数据是完整的帧,在SDRAM中存入了4帧,读取数据总滞后于写入数据2帧,读取完整一帧以后才会去读取下一帧。

由于摄像头所采集到的视频数据存在较多的噪声干扰,在图像识别处理器系统读取数据之前,我们加入了一级邻域滤波器。滤波器基本工作原理为对每一个像素周围8个像素点计算平均值,并与中心像素比较,若差值大于一定范围,则认为中心像素为噪声点,用所计算得到的平均值取代。经过Matlab验证及实际观察,经过滤波后的图像去除了噪声干扰,为图像识别算法的设计提供了极大的便利。经过滤波器以后的图像数据是640×480。

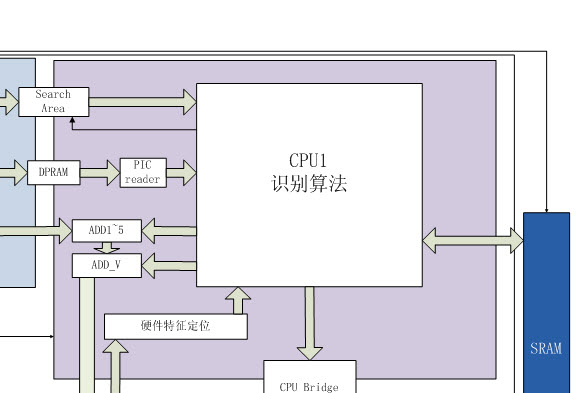

2. 图像识别处理器系统

图像识别处理器系统

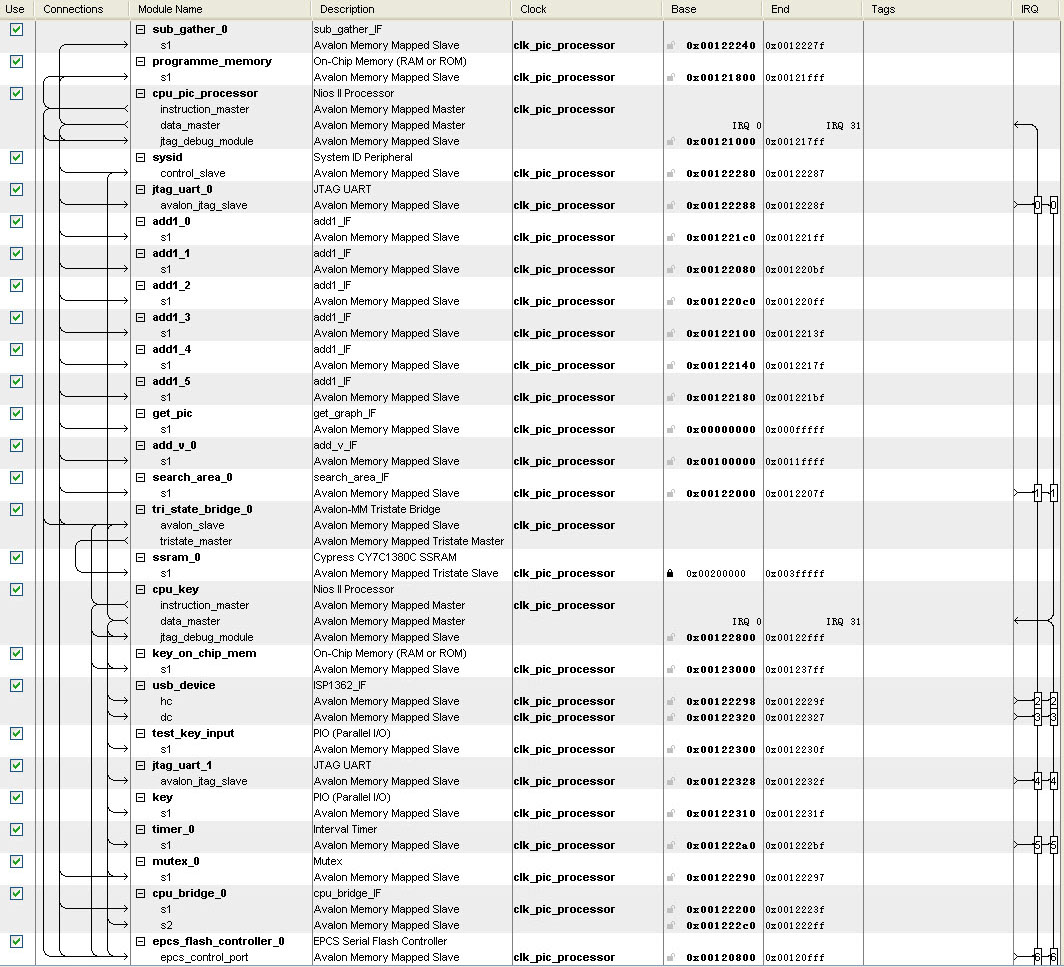

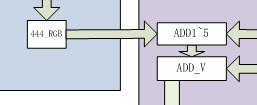

处理器系统的硬件部分主要由PIC reader模块、Search Area模块、ADD1~5模块、硬件帧减加速模块及ADD_V模块组成。由于系统对实时性有极高的要求,处理器很难在很短的时间内处理完一个完整的VGA数据帧,而且系统内存大小的限制也不允许对完整的VGA数据帧进行处理,所以由PIC Reader模块对数据帧像素做一次重新索引,将640*480的VGA数据帧压缩为160*120大小并读入处理器系统。处理器系统经过特征像素提取算法后得到双手及双脚的像素点参考值,将参考值及搜索区域信息写入Search Area模块,由其对存储于SDRAM中的整个数据帧进行搜索,并将搜索到的特征点位置范围返回处理器,然后处理器根据所获得的位置信息执行运动估计算法并将估计的运动范围发送给Search Area模块以获得更新后的特征点位置,通过这种不断交互的方式实现特征点跟踪。处理器系统将特征点位置发送给ADD1~5模块。ADD1~5模块的功能是在特征点标注一个彩色的方框,便于调试和监视。ADD_V模块为一个辅助调试模块,它可以在我们所采用的运动检测算法中在所检测到的运动部分加入标示,便于算法设计及调试。SOPC结构示意图:

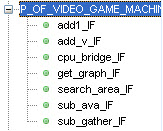

以下为自定义的IP:

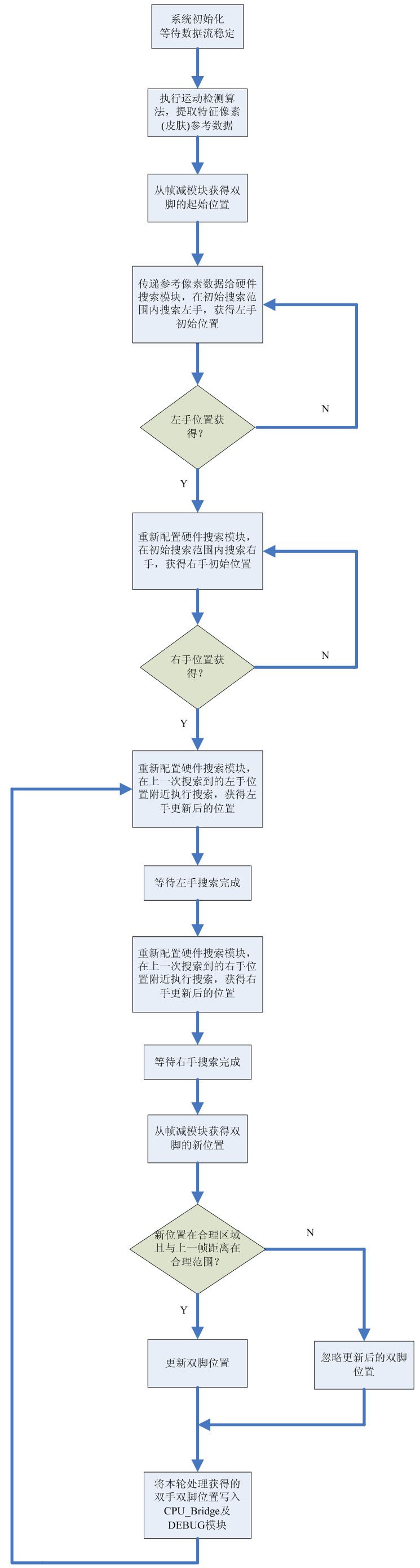

图像识别算法基本流程如下图:

图像识别的基本原理为采集在当前环境下画面中皮肤部分的像素特征值,以此为基准在双手的位置附近进行局部搜索,实现对双手的跟踪。这样,参考像素数据的获取及搜索位置的设定便成为图像识别与跟踪算法的关键。获取参考像素点时,我们采用的方法是已运动检测算法为基础,采集运动图像区域中的合理区域(合理区域的获得见运动检测算法实现部分的描述),求得YUV数据平均值作为一个图像帧的样本。在连续的20帧中,按照同样的方法获取20个参考值,取中间10个参考值并去掉不合理数据(大于200和小于50的值,我们认为是不合理数据)和最大及最小的两个数据后求平均,得到最终的参考数据。在运动检测算法的实现中,我们首先比较联系连续两帧图像数据,若某个像素块(虽然邻域滤波器已经很好的避免了噪声点的干扰,为了增强系统的鲁棒性,算法中还是将相邻几个像素点组成的宏块作为基本处理单位,这样也能提高算法的灵活性)的变化超过一定的阈值,则认为该宏块可能属于运动中的手脚等特征点。但若只依靠相邻两帧作为检测标准则第一帧中被手脚所遮挡的背景像素将成为干扰。所以我们对第二帧和第三帧作同样的处理,并将两次处理所得结果相与,所得到的像素点基本可以认为是所需的特征点,提取其亮度色度等信息作为跟踪时的参考信息。当处理器系统完成参考数据提取后,会将参考数据及搜索范围发送给一个硬件搜索加速器对图像数据进行搜索。初次搜索时,将屏幕划分为四个象限,在每个象限内划出一个较大区域作为初次搜索范围,以保证正确捕获特征点。捕获成功后,后继搜索将在前一次捕获的特征点周围进行,这样既能加快处理速度,减小存储器带宽占用,又能避免图像中可能出现的干扰信息(如非操作者进入画面等)。对于搜索范围大小的确定,一方面需要保证能够实现稳定的跟踪,在双手移到较快的时候不能出现丢失的现象,另一方面又需要避免图像中与肤色颜色相近的物体干扰,保证处理速度,这样就迫使我们在不断的实验中取得一个较好的折中。另外,算法中对搜索位置的确定,使得搜索框尽量处于肤色区域的上端点和左端点(搜索左手时)或上端点和右端点(搜索右手时),保证跟踪的准确和灵敏。对于双脚的跟踪,主要基于硬件帧减模块获取的运动部分的左下端点和右下端点。为了避免身体其他运动部分甚至双脚的互相干扰,只有运动部分在上一次获取值的附近时,才认为新获取的位置信息有效,保证跟踪的稳定性。

3. 动作解析及游戏控制CPU主CPU通过bridge将游戏操作者的特征部位的坐标参数传给协处理器,协处理器根据特征部位的坐标进行动作解析,最终通过USB硬件接驳到PC机进行游戏操控。由于主CPU承担了比较繁琐重的任务,而且为了后绪功能扩展。我们利用协CPU进行操作者动作的解析及游戏控制。为了保证解析的稳定性,需要尽量减小主CPU传递的参数的抖动影响。辅助CPU主要完成两个任务,第一是动作解析;第二是游戏控制。使用MicroC/OS-II RTOS来管理这两个任务,游戏控制的优先级高于动作解析。测试时采用了竞速类游戏作为演示平台,此类游戏对于实时性要求较高,再结合此类游戏的特点进行了优化。

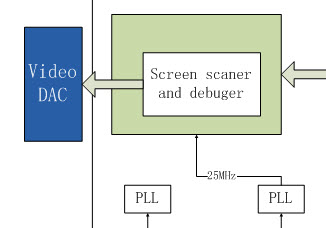

4. 调试与监视模块

调试与监视模块

它的主要功能是根据摄像头捕获的图像以及前述处理模块产生的调试数据产生VGA扫屏时序,将图像与调试标注显示在监视屏幕上。

调试数据一部分来自图像处理器系统的ADD1~5模块。处理器系统捕获和跟踪特征点时,会将特征点位置发送给ADD1~5模块,ADD1~5模块会在该区域划出一个方框,覆盖由摄像头获取的图像数据,这样在监视屏上实现了特征点的实时跟踪显示。另一部分来自图像处理器系统的ADD_V模块。处理器在执行运动检测算法时,将检测出的图像变化区域即运动区域生成一副二值图像并发送给ADD_V模块,ADD_V模块根据此图像生成一个掩膜板将摄像头捕获的图像中该区域遮蔽,这样在监视屏中就可以监视运动检测算法的正确与否。

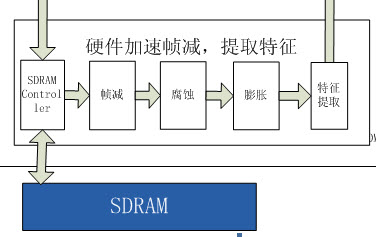

5. 硬件帧减为了获得帧间信息,捕获图像运动信息,需要进行帧减运算,这将占用巨大的CPU资源,所以我们设置了一个硬件帧减模块,为了抑制噪点,我们将帧减以后的数据进行腐蚀和膨胀,从matlab分析来看,该算法能较好的抑制噪声。在经过上述一系列的计算以后,为了进一步降低CPU的负担,我们使用一个八方形去提取运动参数,这样CPU只需去查询提取到的结果。6. 硬件搜索硬件搜索利用第一块SDRAM提供的原始数据,在原始图像数据中搜索敏感数据区域,主CPU将搜索条件,包括搜索坐标、宽度等条件发送给硬件搜索模块,硬件搜索模块根据搜索条件进行匹配,当搜索完毕,硬件搜索模块向CPU发送中断请求。并返回搜索的结果。(Revision: 7 / 2010-08-28 19:14:46)

5. 设计方法 (Final Project Paper)

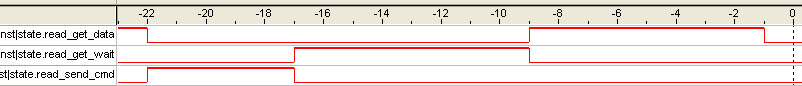

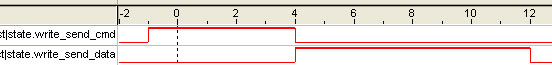

2. 根据开发板资源细化设计方案,制定详细的软硬件设计架构,进行任务分工。Altera所提供的SOPC设计方法与工具是我们进行软硬件划分及任务分配的重要依据。我们设计中需要对大量的视频数据进行处理及调度,对与存储器及其接口方面要求有极高的鲁棒性和较高的性能。Altera所提供的存储器控制IP核能够很好的满足我们的设计要求。我们的设计中对于软件算法有较高的要求。在视频数据处理算法中要求算法有较高的效率以满足实时性要求。Altera提供的NIOS处理器能够高效率的执行算法,而且其完整的SOPC设计方法与规范使我们能够方便地开发硬件加速单元,获得更好的软硬件划分方案,在性能与资源开销之间获得非常好的折中。SOPC设计方法学能够极大的提高设计生产率,使我们能够尝试搜索更大的设计空间,给出更合理的设计方案。3. 设计与调试图像捕获硬件逻辑,并根据实际捕获的图像效果设计修改算法规范。借助Matlab分析工具设计图像增强硬件逻辑,一方面提高了系统鲁棒性,另一方面减小了软件算法复杂度,提高了算法执行效率,提高了系统性能。基于FPGA的SOPC设计方法学,可以将复杂的硬件功能实现在单一的芯片中。高质量的Altera器件能够保证硬件逻辑性能,且与软件系统有紧密的耦合。4. 搭建算法所需硬件环境,设计图像识别算法,根据实际运行结果不断进行优化,必要时对功能重新进行软硬件划分。5. 搭建USB键盘控制逻辑及控制软件系统所需硬件环境,设计USB虚拟键盘控制程序。6. 系统联调,扩展系统功能,优化系统性能。7. 在altera提供的SDRAM controller的基础上,我们修改了两中SDRAM Controller,第一个是用在图像解码处,SDRAM controller提供三个接口如下图所示:其中原始图像输入和重组后的图像输入的优先级较高,随机访问的优先级较低,随机访问都是burst8的模式访问。随机访问用在接驳图像搜索模块。该SDRAM频率运行在108MHz。为了提高SDRAM的访问效率,全部采用burst8模式进行读写。经过测试,写入数据的效率大概为61.54%,读出数据的效率大概为38.10%。实测SDRAM读出情况实测SDRAM写入情况摄像头输出的数据比需要的数据大,为了减小对存储器的压力,在数据存入存储器之前就将数据裁剪为656×482。按照计算写入的数据流为656×482×25,读出的数据流为656×482×60,这样存储器还有大约45M的空余周期留给随机访问,如果按照随机搜索每次搜索100×100的图像区域,可提供1714次搜索的能力,完全能满足每秒处理60帧图像的能力。第二个SDRAM controller用在硬件帧减处,提供4个接口,示意图如下:当前输入图像和前4帧图像的位置由SDRAM controller自动调度,在存储器中存入8帧图像,当前输入图像和读出的前4帧图像的位置差4帧。随机读写访问,提供程序的接口和其他的访问请求。存储器每秒需要写入640×480×60和读出640×480×60的数据,该SDRAM频率运行在108MHz。写入数据总共占用了30M周期,读出数据占用了49M周期。8. DE2-70片上具有一块SSRAM,在本设计中使用该SSRAM作为两个NIOS II的程序存储器,两个CPU各分得1M的容量。9. 为了使CPU能够直接读取图像数据,我们使用FPGA片上sram开辟了5块4096×24的存储区域用来存储160×120的图像数据;另外为了调试方便,我们开辟了一个二值存储区域来存储CPU发送过来的图像映射,外挂硬件模块将把该二值映射直接输出到屏幕。片上M4K总共有250块,使用其中的206块。10. 为了提高设计的运行速度,我们使用了logic lock,将主要的模块(如两个CPU)指定在特定的位置上。达到设计的108MHz,使用logic lock之前的速度为98.36MHz,使用logic lock以后的速度为115.82MHz。

(Revision: 4 / 2010-08-28 19:33:49)

6. 设计特点 (Preliminary Paper)

1. 系统硬件结构复杂,且时序要求严格,各个模块工作时钟不同,对时钟树设计要求较高。Altera EP2C70器件提供4个PLL,为时钟设计提供了极大的方便。

2. 在本设计中涉及到大量的图像的存储及处理,系统需要大量的数据调度,对存储系统需求较大。有的部分需要很高的访问效率,比如CPU对图像数据的访问,因为CPU对图像数据的访问效率比较频繁,所以需要较高的效率,此时采用内部存储器。EP2C70 提供总共1,152,000 bit的片内存储容量,保证了数据调度的实时可靠。在图像剪裁以及调整和帧减时,由于这些过程的数据完全由硬件操作,访问效率高,但是对存储器容量要求高,不可能在内部实现,所以使用外部存储器;DE2-70提供了很丰富的外部存储器,在设计中使用了板上的两片SDRAM。为了使CPU更高效的运转,而且两个CPU的程序也比较大,综合考虑效率和容量,我们采用外部SRAM来存放CPU的指令。片外SRAM的使用大大减小了对片内存储器的压力。3. 系统要求软硬件协同工作,需要两个高性能CPU及大量的硬件逻辑,要求FPGA有足够的逻辑资源。EP2C70共有68,416个逻辑单元,保证逻辑资源足够,使系统性能定义时有更大的灵活性。4. 采用摄像头捕获的数据干扰较大,噪声点严重,设计中用matlab设计了一个邻域滤波器,并用硬件实现,完成了对噪点的硬件过滤,极大得简化了软件算法复杂度,提高了算法的实时性能,增强了系统的鲁棒性。5. 图像处理中运动帧估计算法的帧剪除及匹配特征点搜索部分算法简单,但数据量极大,若用软件算法实现性能开销难以承受。我们通过硬件实现两个自定义外设完成这两项工作,大大提高了算法效率与性能。6. 在USB设备的控制CPU中,使用MicroC/OS-II RTOS对解析以及键盘控制两个任务进行统一管理,简化了程序开发及任务管理。(Revision: 4 / 2010-08-28 19:15:14)

7. 总结 (Final Project Paper)

通过本次大赛,我们对Altera的集成开发环境及cyclone器件有了更深刻的了解,Altera集成开发环境是一个非常容易上手的软件;人性化的设计、强大的功能使得设计者能够在短时间之内快速完成设计。SOPC builder等软件能够让用户在很短的时间之内构建复杂而稳定的系统,同时提供的软件开发环境eclipse,为用户提供了一整套完整的SOPC解决方案。Cyclone系列芯片具有很高的性价比,结合logic lock等软件,能够进一步提升芯片的性能,同时能提高综合、布线的速度;特别是对于较大设计的后期调试有很大的帮助。(Draft / 2010-08-28 09:50:01)

.jpg)