Profile - CN574

CN574

安全数码伴侣

信息工程大学电子技术学院信息安全系

Project

Name of Project: 安全数码伴侣

Contact Information

Name: 程建雷 E-Mail: chengjian066@163.com Telephone: 037181638652 Mobile Phone: 13838269932 Mailing Address: 河南郑州管城区商城东路12号电子技术学院3系304教研室

Contest Advisor

Name: 徐进辉 E-Mail: xusamuel@gmail.com Telephone: 15037151808

Members

No. Name English Name 1 程建雷 chengjian066@163.com Cheng JianLei 2 李洪鑫 lihongxin1986@126.com Li HongXin 3 常忠祥 changzhongxiang0@126.com Chang ZhongXiang

Project Paper - view as Preliminary(2009/06/15), Final(2009/09/14), Draft, Latest

1. 设计概述 (Preliminary Paper)

1.1设计意图数码伴侣即数码相机伴侣,是一种大容量便携式数码照片存储器,其基本特点是:第一,以大容量移动硬盘的存储机制来存储数码照片;第二,存储过程无需电脑支持;第三,提供简洁明了的数据处理方式。因此,当前市场上的数码伴侣产品多采用“多功能读卡器+大容量移动硬盘+液晶显示器”的设计模式。随着数码产品的迅猛发展,出现支持OTG(On-The-Go)技术的数码伴侣,使得数码伴侣的功能日益完善,应用范围更为广阔。而伴随数码伴侣的逐步普及,数码伴侣的安全性备受关注。目前数码伴侣产品的安全性主要是数据的完整性,即保证存储卡中数据完整、正确地备份到数码伴侣的内置硬盘中,而对数码伴侣中数据的机密性缺乏安全保证,用户数据采用明文存储。这种潜在的安全隐患限制了数码伴侣在对安全性有较高要求的场合使用,例如,数码伴侣用户不宜在其中存储个人隐私数据或是商业机密信息,因为在多用户共用一个数码伴侣或者不慎丢失的情况下,其中存储的敏感数据可被他人轻易获取,从而对用户的个人隐私或者商业利益造成损害。因此,安全性的增强是数码伴侣功能进一步完善、在更大范围内普及应用所必需考虑的问题。针对这种需求,本文设计了一款安全数码伴侣,该作品的设计模式可以表示为:“存储卡读卡器+大容量移动硬盘+触摸屏(LTM)+安全模块”。与传统数码伴侣显著区别在于两个方面:第一,安全模块可有效保护用户数据的机密性,并实现多用户身份认证。本作品中用户数据在数码伴侣中以密文形式存储,采用的加密算法为AES(Advanced Encryption Standard),即美国标准技术研究所(NIST)主持开发的作为联邦信息处理标准的数据加密算法。用户可以有选择地对存储卡中的数据先加密再存储到数码伴侣中,从而保证了用户数据的机密性。安全数码伴侣集成高灵敏度指纹传感器,采集用户生物特征指纹,经过SHA-1(Secure Hash Standard)杂凑产生加密的密钥,并将指纹作为合法用户身份的唯一标识。通过指纹匹配,对用户身份进行认证,判断用户的合法性,实现用户管理。第二,新颖的LTM搭配数码伴侣使用,为用户提供更便捷的操作方式。本作品采用LTM,且基于µC/GUI自主开发用户图形界面,用户可以通过简单的操作,完成以下工作:(1)指纹登录,使用数码伴侣的安全功能;(2)浏览存储卡以及硬盘中的图片(包括加密图片与未加密图片);(3)将存储卡中的图片加密后存储至硬盘;(4)添加、删除用户,更换用户密钥。另外,本作品利用ISP1362芯片开发主从USB设备接口,实现数码伴侣与主机、数码伴侣与U盘间的数据传输,提高了产品的灵活性。本作品是在NiosII双处理器的平台上利用嵌入式操作系统µC/OS-II实现一款安全数码伴侣,将嵌入式系统设计技术与现代密码技术进行了有机结合,增强了数码伴侣产品的安全性,提高了操作控制的灵活性,具有较好的实用前景和较高的推广价值。1.2适用范围及用户群随着数码产品走进每个人的生活,只要有数码相片的地方都可以使用本作品。拥有普通数码产品和安全存储的双重功能,作品能够广泛应用于社会的各个领域。对于普通的使用者来说,不论是在工作或外出旅游都可以携带在身边,实时地进行图片的浏览与移动,满足用户的各种需求。特别地,本作品在安全领域具有自己独特的优越性。通过硬件加密的方法实现图片的安全存储,能在保证实用性的前提下有效防止非法用户对硬盘中涉密图片的各种操作。对于存储秘密信息的数码伴侣,即使丢失或者被攻击,只要没有正确的密码,持有者就无法浏览硬盘中的加密图片,这样能够较好地保证数码伴侣的安全,满足像政府、金融、证券、税务等信息安全级别高的部门的要求。本设计是基于图形界面开发、支持多用户安全操作的数码伴侣。与大多数的数码产品相比,本设计实现了图片安全存储功能,提高了操作控制的灵活性,具有很高的应用价值和广阔的市场前景。1.3本设计采用本款Altera器件设计的原因Altera的Cyclone II EP2C20器件保持了用户定义的功能、业界领先的性能和低功耗等Cyclone架构的特色和优势,采用了更为先进的工艺设计,能够满足系统各个方面的要求,尤其在性能方面更具有显著的优势:(1)丰富的嵌入式存储器。Cyclone II EP2C20器件内包含52个M4K RAM块,每个存储器块包括512个校验比特,可以提供多达200Kb的片内存储器,这为嵌入式系统的程序运行提供了足够的内存空间,极大地提高了系统吞吐率,满足了大量数据交互的实时性要求。(2)专用的外部存储器接口。Cyclone II器件能够与外部存储器进行高速可靠的数据传输,支持单倍数据速率(SDR)、双倍数据速率(DDR)、DDR2、QDRII,其宽度可达36位,频率可达200MHz。设计中使用片外SDRAM作为双处理器间交互数据的存储器,其高速的数据传输速率有效地缩短了图片显示的延迟,使图形界面操作响应更加及时,保证了作品的性能。(3)循环冗余码(CRC)自动校验。Cyclone II EP2C20器件内部提供了片内CRC自动校验电路,无需任何额外成本或复杂外部逻辑即可在所有设计中轻松地实现CRC校验。本设计中存在大量的数据传输,采用CRC校验,增加了数据传输的可靠性,从而最大限度的降低了外界干扰造成的错误。(4)高性能的I/O标准。Cyclone II EP2C20器件支持多种单端和差分I/O标准,如HSTL、PCI-X、LVPECL、LVCMOS,而单端I/O标准是FPGA与高级存储器连接使用的关键因素。系统设计使用片外存储器存储程序代码、用户密钥及图片数据,这款器件能够很好地满足系统需求。(Draft / 2009-06-15 19:04:35)

2. 功能描述 (Final Project Paper)

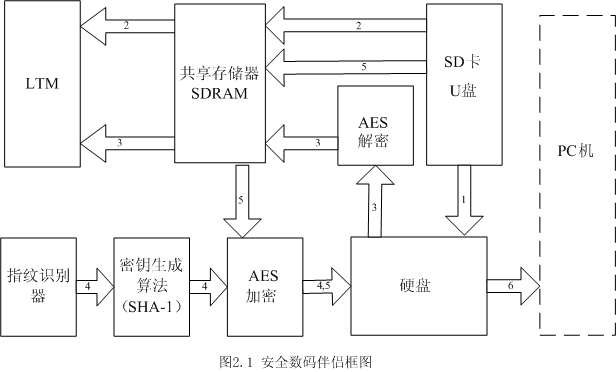

安全数码伴侣所能实现的功能如上图所示:1. SD卡或USB设备中的图片不经加密直接转存到硬盘中(如箭头1所示)。2. SD卡或USB设备中的图片数据,首先经过CPU_I存入共享SDRAM,然后通过CPU_II将图片在LTM上实时显示(如箭头2所示)。3. 硬盘中的图片密文数据,经过AES解密后存入共享SDRAM,然后经过CPU_II将图片在LTM上实时显示(如箭头3所示)。4. 指纹识别器录入的指纹信息,经杂凑算法(SHA-1)生成指纹信息摘要,并从中提取部分摘要值,作为用户的加密密钥(如箭头4所示)。5. 根据LTM上的图形操作界面的提示,选择对当前所浏览图片的操作。若选择加密,则共享SDRAM中的数据经AES加密后存入硬盘(如箭头5、(4,5)所示)。6. 通过PC机端操控界面,直接转存和浏览硬盘中的图片(如箭头6所示)。通过嵌入式操作系统提供的图形界面操作,实现对存储图片的浏览和移动。不仅能有选择地对存储在硬盘中的图片进行加解密,而且能利用指纹信息完成对不同用户的身份认证。采用杂凑算法SHA-1对指纹信息进行杂凑运算产生160-bit的指纹摘要值,从中提取128-bit作为加密密钥。硬盘数据加解密操作采用AES算法,同时在Cyclone II FPGA上实现了硬盘ATA接口,支持PIO的五种传输模式与DMA的三种传输模式,有效降低了由于加解密操作所带来的系统性能损失。设计了USB到硬盘ATA接口的转换电路,方便了数码伴侣与USB设备的数据传输,增加了作品的可用性。在作品各个功能的实现过程中,考虑到产品的实用性,对双核进行了合理的功能划分,并依靠嵌入式操作系统μC/OS-II来调度各功能模块的任务,实现了各个任务的有序运行及彼此间的协调配合,而这对用户来说完全是透明的,方便了用户操作,提高了系统的可应用性。

(Revision: 2 / 2009-06-15 19:18:49)

3. 性能参数 (Final Project Paper)

(1) 电源:

直流电压:5V

工作电流:800mA

(2) 环境:

工作温度:0~60C

相对湿度:8%~95%

(3) LCD刷新速度

刷新频率:<5ms

显示速度:<10ms

(6) AES加解密速度

AES加解密最大工作频率:300MHz

AES加解密吞吐率:44.8Mbps

(7) SHA-1杂凑速度

SHA-1杂凑最大工作频率:350MHz

SHA-1杂凑吞吐率:210Mbps

(8) 系统资源占用

Device EP2C20F484C7

Total logic element 4824

Total register 2776

Total pin 128

Total memory bit 168064

Total PLL 1

Performance 50Mhz

上述参数都是本系统实际的性能参数,完全实现了设计的功能和参数要求。

本设计采用了双NIOSII核的处理方式,Altera的CycloneII器件提供了强有力的硬件支持,特别是将NIOSII软核处理器溶入以后,将FPGA的功能从单一地做一些并行、高速、逻辑性强、时序简单、操作繁琐的工作进行了极大的扩展,把以往需要外部控制单元做的工作全部集成到一片FPGA中,并且内部NIOSII软核的多种外设接口都可以随时删减与添加。同时,NIOSII软核针对低速控制、外设访问复杂、外设众多、修改频繁的工作具有极强的适应能力,而且正好与FPGA I/O口众多的特点相一致,使得软硬件的设计过程中不用再单独考虑FPGA和控制单元的工作协调及接口问题,所有数据处理、命令控制、时序协调、并行串口、低速高速设计都集中到一片FPGA中,利用它众多的I/O口,简单地完成系统设计和软件编程。

(Draft / 2009-09-14 14:23:32)

4. 设计结构 (Preliminary Paper)

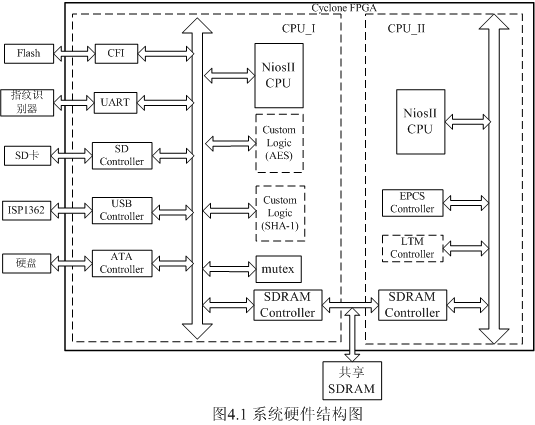

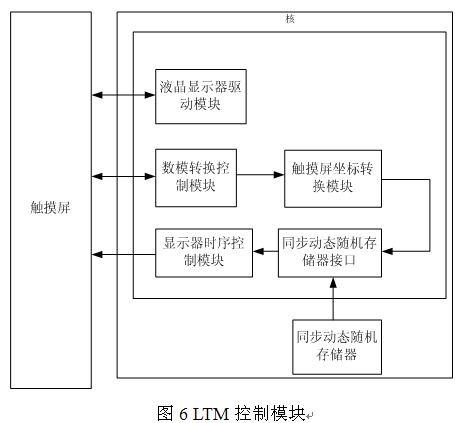

4.1系统整体框图安全数码伴侣主要是由双NiosII处理器、SD卡控制器、ATA接口控制器、LTM控制器、USB控制器、指纹识别控制器、AES加/解密模块及密钥生成模块等构成,如图4.1所示。1. SD卡控制器:通过NiosII的并行输入输出口(PIO),以命令方式实现4线SD模式读操作,最大传输速率可达到12.5MB/S,从而保证对SD卡中存储图片的浏览和移动能够高效地完成。2. LTM控制器:采用硬件实现方法设计了LTM与开发板之间的接口,主要包括液晶显示器驱动模块、数模转换控制模块、触摸屏坐标转换模块、显示器时序控制模块、同步动态随机存储器接口模块以及缓存控制模块,保证了数码伴侣的各种界面操作的顺利实现。3. ATA接口控制器:考虑到接口模块与系统交互的实时性,采用了Cyclone II FPGA内部可编程逻辑资源,设计了相应的读写时序发生器,完成硬盘与主控制器间的数据交换,能够支持PIO读写的五种模式与DMA读写的三种模式。4.USB控制器:基于DE1开发板丰富的外设扩展接口,利用ISP1362接口芯片开发主从USB设备接口,通过配置实现ISP1362不同的工作模式,从而完成数码伴侣与主机、数码伴侣与U盘间的数据交互,方便了用户的操作,进一步提高了作品的实用性。5. AES加/解密模块:利用NiosII处理器强大的运算功能,同时充分发挥C2H工具的硬件加速特性,以自定义指令的方式实现了AES算法。通过分析AES算法,提取了算法中最耗时的关键模块,自定义相关的硬件外设进行加速,使AES算法的核心工作频率达到400MHz。6. 密钥生成模块:考虑到系统的安全性,结合现代密钥管理的思想,利用NiosII处理器实现了对指纹信息的杂凑,并在片外Flash 中为不同用户的指纹摘要值分配不同的存储空间,不仅支持多用户的操作,还保证了只有合法用户才能正确地进行图片浏览与加解密操作。杂凑算法SHA-1也是通过自定义指令的方式实现的。7. 指纹识别器:利用NiosII对外部设备的强大控制能力,通过UART接口,采用命令模式对杭州中正公司的SM-620指纹识别器进行控制,完成指纹登录、指纹比对以及模板上传等操作,为加解密算法提供了密钥。

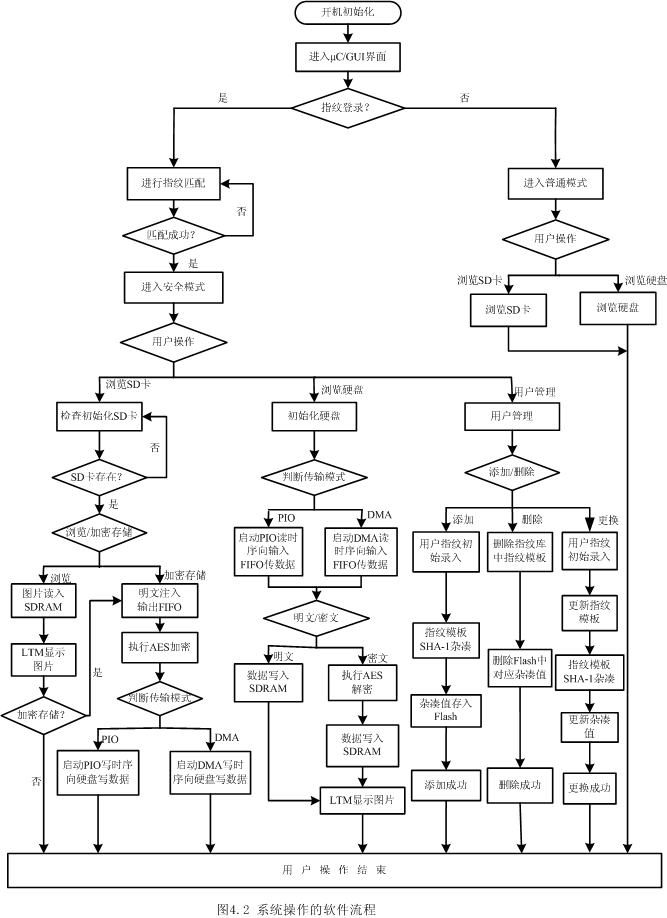

4.2软件流程系统软件任务主要包括SD卡读任务、硬盘读写任务、加解密任务、用户管理任务、图片浏览任务、LTM显示任务等。系统启动后,操作界面会提示是否进行指纹登录。如果选择否,则只能进行SD卡与硬盘图片的浏览和移动,完成普通数码产品的功能。如果选择是,则进入安全模式,完成图片的加解密存储功能。安全模式下的用户操作主要包括SD卡和U盘图片浏览、硬盘读写操作及用户管理三个部分。SD卡浏览任务主要实现SD卡中存储文件的浏览与加密。当系统检测到SD卡时,便可以通过LTM对存储卡进行相应的操作。如果选择加密图片,则CPU_I向SD卡发送命令将数据读入输出FIFO中,并启动AES加密算法,在完成数据的加密操作后,根据硬盘状态启动PIO或者DMA写时序发生器,将密文写入硬盘中。如果选择浏览图片操作,则将数据读入共享存储器SDRAM中,此时CPU_II通过读SDRAM可完成LTM显示功能,此时仍可选择是否加密存储,如果是,则将共享存储器SDRAM中的数据写入输出FIFO,具体过程同上。U盘浏览任务同SD卡。硬盘操作流程主要是实现硬盘中存储文件的浏览与加密。当用户读取到硬盘的文件列表时可以通过LTM完成对硬盘的各种操作。在浏览硬盘中图片时,CPU_I根据硬盘状态可以启动PIO或者DMA读时序发生器将数据送入输入FIFO中。如果是明文数据,则直接写入共享存储器SDRAM中,CPU_II通过读SDRAM实现图片在LTM上的显示。如果是密文数据,则启动AES解密算法。解密完成后将数据写入SDRAM,此时LTM可显示解密后的图片。用户管理主要实现用户的添加、删除及工作密钥的更换。如果添加一个新用户,则需要进行指纹的录入,并通过SHA-1杂凑生成160-bit的指纹摘要,存入片外Flash中。如果删除一个用户,则不仅清除其指纹模板,还需删除相应密钥值。如果更换工作密钥,则需要更新指纹模板和指纹杂凑值。(Revision: 2 / 2009-06-15 19:16:33)

5. 设计方法 (Final Project Paper)

5.1 SD卡存储模块

5.1.1 SD卡控制器

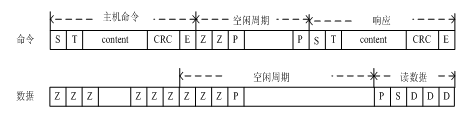

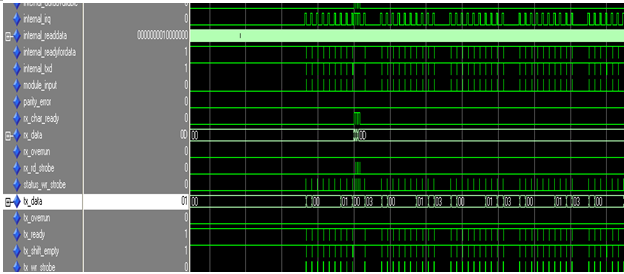

SD卡控制器主要是产生读SD卡操作时的各种时序信号,包括命令信号、时钟信号及数据流。DE1上的SD接口为1线SD模式,速度受到了很大限制。为了满足系统性能的要求,我们把SD卡的读模式改为4线SD模式,一次可以读取1~512Byte的图片数据,最大传输速度可达到12.5MB/S。4线SD模式的读时序如图所示。

读命令结束后,数据从SD卡开始传输。经过最小为2个周期的延时,SD卡对命令进行响应。数据的正确性采用CRC校验保护。

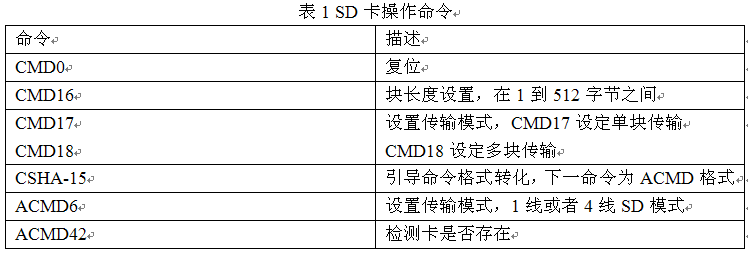

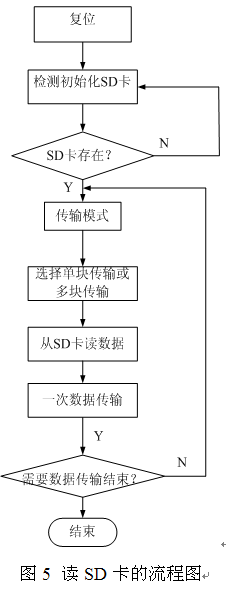

SD卡读操作只需要几条命令,如表格1所示。

SD卡的读流程如图5所示。

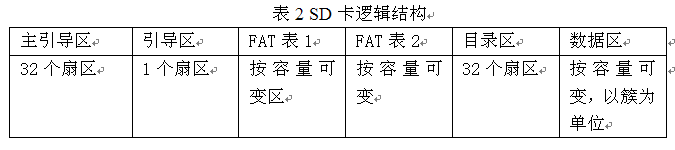

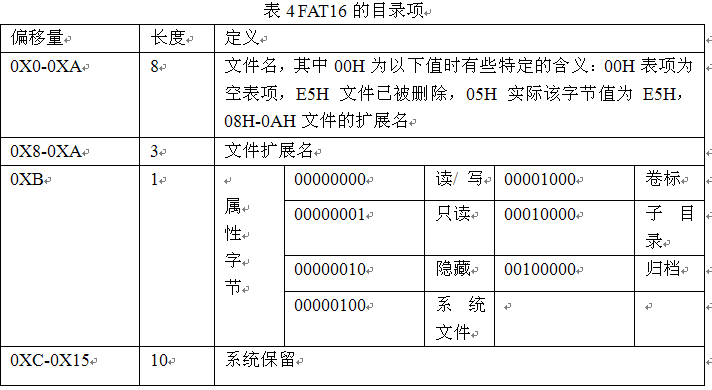

5.1.2 FAT16文件系统

SD卡的结构与硬盘类似,文件格式为FAT16,所以在格式化时,系统采用了FAT16 文

件格式。下面结合所使用的SD卡介绍文件系统原理。

1. MBR(Main Boot Record)按其字面上的理解即为主引导记录区,位于整个硬盘的0磁道0柱面1扇区。不过,在总共512字节的主引导扇区中,MBR只占用了其中的 446个字节(偏移0--偏移1BDH),另外的64个字节(偏移1BEH--偏移1FDH)交给了DPT(Disk Partition Table硬盘分区表)(见下表),最后两个字节"55,AA"(偏移1FEH- 偏移1FFH)是分区的结束标志。这个整体构成了硬盘的主引导扇区。

主引导记录中包含了硬盘的一系列参数和一段引导程序。其中的硬盘引导程序的主要作用是检查分区表是否正确并且在系统硬件完成自检以后引导具有激活标志的分区上的操作系统,并将控制权交给启动程序。MBR是由分区程序(如Fdisk.com)所产生的,它不依赖任何操作系统,而且硬盘引导程序也是可以改变的, 从而实现多系统共存。

偏移 长度 所表达的意义

0 字节 分区状态:如0-->非活动分区

80--> 活动分区

1 字节 该分区起始头(HEAD)

2 字 该分区起始扇区和起始柱面

4 字节 该分区类型:如82--> Linux Native分区

83--> Linux Swap 分区

5 字节 该分区终止头(HEAD)

6 字 该分区终止扇区和终止柱面

8 双字 该分区起始绝对分区

C 双字 该分区扇区数

2.DBR区

DBR (Dos Boot Record)是操作系统引导记录区的意思。它通常位于硬盘的0磁道1柱面1扇区,是操作系统可以直接访问的第一个扇区,它包括一个引导程序和一个被称为 BPB(Bios Parameter Block)的本分区参数记录表。引导程序的主要任务是当MBR将系统控制权交给它时,判断本分区跟目录前两个文件是不是操作系统的引导文件。如果确定存在,就把其读入内存,并把控制权交给该文件。BPB参数块记录着本分区的起始扇区、结束扇区、文件存储格式、硬盘介质描述符、根目录大小、FAT个数,分配单元的大小等重要参数。

3.FAT区

FAT16 是用 2 个字节(16 位)来描述一个簇的,所以这时 FAT 表的大小就应该是2位的簇数个字节。FAT表中,第 4,5个簇表示第2个簇,第 6,7 个字节表示第3个簇,第8,9字节表示第4个簇……。就这样,每一个簇都有两个和它对应的字节。这两个字节里面存放的数据就是下一个16K 数据所在的簇号。2个字节最大能表示 65535,一个簇最大为32K,所以 FAT16最多能给65565*32K≈2G。这就是FAT16格式为什么分区不能大于2G 的原因。实际上,并不是所有的数值都代表簇号,有几个值被赋于了特定的含义,

我们先看看这几个特殊值代表的含义。序号 数值 含义

1 FFF8 磁盘标识字

2 FFFF 第一簇已经被占用

3 0000 未使用的簇

4 0002-FFEF 使用的簇

5 FFF0-FFF6 系统留的,一般不会出现这几个簇号

6 FFF7 坏簇,在写文件时不能向它里面写

7 FFF8-FFFF 表示这是最后一簇,文件到此结束了

由于FAT对于文件管理的重要性,所以FAT有一个备份,即在原FAT的后面再建一个同样的FAT。初形成的FAT中所有项都标明为"未占用",但如果磁盘有局部损坏,那么格式化程序会检测出损坏的簇,在相应的项中标为"坏簇",以后存文件时就不会再使用这个簇了。FAT的项数与硬盘上的总簇数相当,每一项占用的字节数也要与总簇数相适应,因为其中需要存放簇号。

由于每个簇的存储空间最大只有32KB,所以在使用FAT16管理硬盘时,每个分区的最大存储容量只有(65536×32 KB)即2048MB,也就是我们常说的2G。现在的硬盘容量是越来越大,由于FAT16对硬盘分区的容量限制,所以当硬盘容量超过2G之后,用户只能将硬盘划分成多个2G的分区后才能正常使用。

4.DIR区(根目录区)

DIR(Directory)是根目录区,紧接着第二FAT表(即备份的FAT表)之后,记录着根目录下每个文件(目录)的起始单元,文件的属性等。定位文件位置时,操作系统根据DIR中的起始单元,结合FAT表就可以知道文件在硬盘中的具体位置和大小了。

5.数据(DATA)区

数据区是真正意义上的数据存储的地方,位于DIR区之后,占据硬盘上的大部分数据空间。

5.2 LTM控制器

LTM控制器主要设计了五个控制模块实现图片的浏览及加密功能。

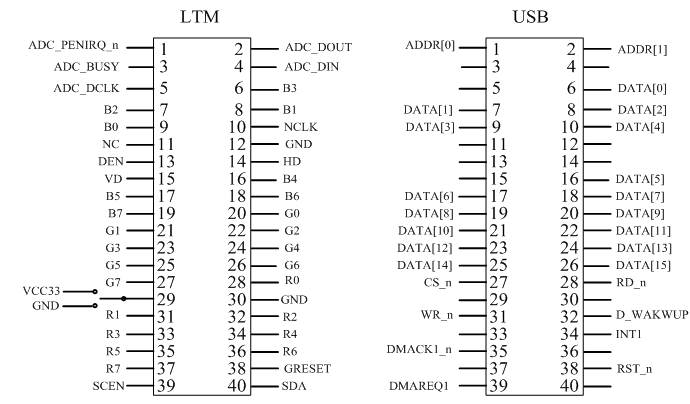

如图6所示,液晶显示器驱动模块驱动LTM工作,数模转换控制模块和触摸屏坐标转换模块确定触摸屏的坐标位置和所要执行的命令,同时提示同步动态随机存储器接口模块从SDRAM模块中读取所需要的数据。显示器时序控制模块用来控制在LTM的实时显示功能,下面对主要模块的时序进行简要介绍。

5.2.1驱动模块

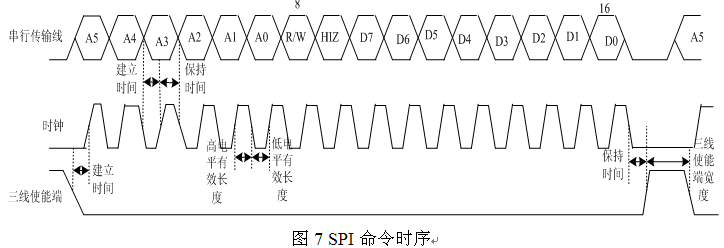

如图7所示,驱动模块采用的是串行外围设备接口(Serial Peripheral Interface,SPI)模式,其中前六比特(A0~A5)是地址信息,紧接着一个比特(R/W)控制读写命令(0表示写,1表示读),第八个周期(HIZ)为空闲周期。最后八比特(D7~D0)为要传输的数据。数据为串行输入,从高位到低位依次传输。当检测到第十六个周期的上升沿后,数据将写进已分配好的地址。

5.2.2显示模块

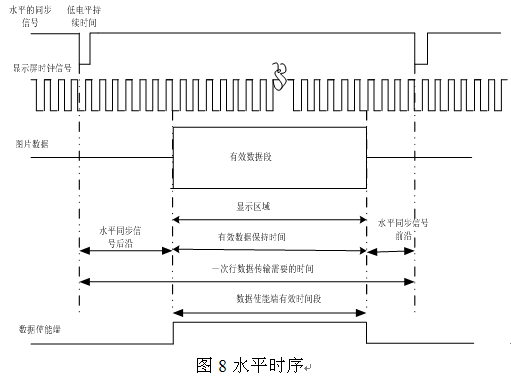

水平同步输入信号有一段持续的低电平,这个信号是作为一组数据传输的结束和另一组数据传输开始的标志信号。图像原始数据在水平同步时序后沿一段时间内是无效的,这段时间后才是真正的有效数据。在有效数据传输时间段内数据信号使能端为高。最后,下一组数据开始之前也有一段为数据无效期。同时数据使能端直到下一组有效数据传输时才置高。如下图所示。

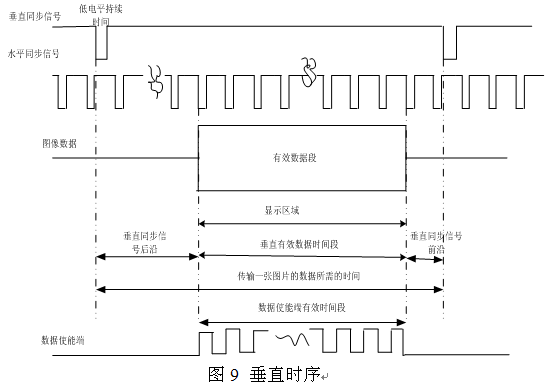

垂直时序由多个水平时序构成,垂直同步信号控制数据传输的开始和结束。垂直同步信号的一段持续低电平同样作为一组数据结束和下一组数的开始的标志。如下图所示。

5.2.3坐标转换模块

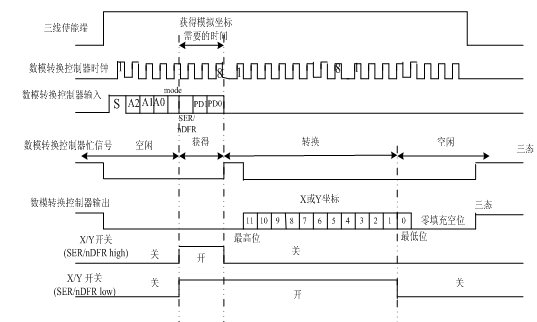

由于扩展槽接口有限,所以显示屏驱动模块和坐标转换模块共用一个时钟源和三态使能端。为了防止两者混淆,所以三态使能端高时时钟源为数模转换模块使用,低电平时时钟源为显示屏驱动模块使用。数模控制器输入端口向AD7843发出需要的命令,从而使数模控制器输出所需要的坐标,每得到一个坐标需要二十四个周期,所以要得到完整的坐标,至少要经过五十个时钟周期。

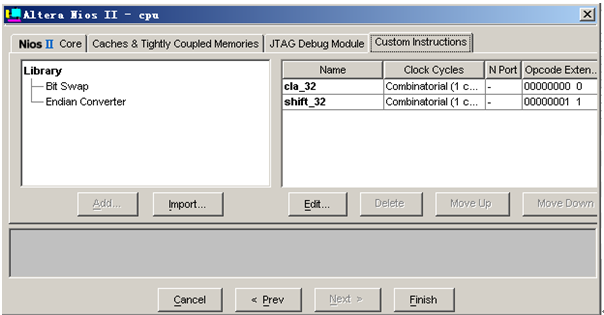

5.3自定义指令

NiosII软核处理器最大的特点是灵活,用户可以方便地增加指令,其它SOC系统是做不到的。通过定制用户指令,系统设计者可以把系统中用软件处理耗费时间多的关键算法用硬件逻辑电路来实现。NiosII的定制指令是与CPU 的数据通路中的ALU相连的用户逻辑块,基本操作是:接收从dataa和/或datab端口输入的数据,经过定制指令逻辑的处理,将结果输出到result端口。

本设计数据加解密算法采用AES算法,杂凑算法采用SHA-1算法,并用自定义指令的方法对算法中的关键模块进行硬件实现,从而有效的优化软件算法的执行速度,大大提高了系统的效率。

5.3.1 AES加解密算法设计与实现

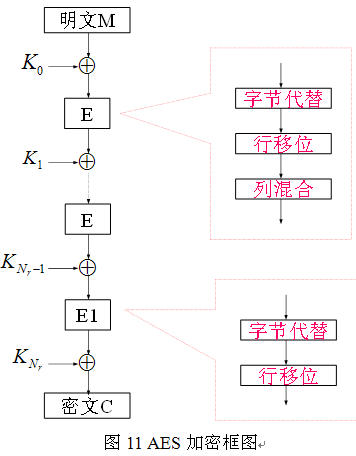

高级加密标准(Advanced Encryption Standard,AES)是美国国家标准技术研究所主持开发的作为新的联邦信息处理标准的数据加密算法,集安全、性能、效率、可实现性及灵活性于一身,能抵抗目前已知的所有攻击,能在各种平台上快速地实现,并且具有良好的并行性。AES分组密码算法采用代替-线性变换网络,以字节代替和线性变换为基本变换环节,经过多次迭代来实现混乱和扩散。字节代替(8比特输入8比特输出的S盒)变换是算法中唯一的非线性变换,起到混乱和局部扩散的作用,是AES的核心;线性变换(行移位变换和列混合变换)使状态矩阵按行移位、按列混合,起到了整体扩散的效果。本设计中的AES加密算法分组长度为128比特,密钥长度也为128比特,迭代圈数Nr为10圈。AES加密的框图如图所示。

待加密的128比特的明文分组首先作为输入状态用状态矩阵(4×4的字节矩阵)表示出来,接着与初始圈子密钥相加,然后进行Nr圈迭代,除第Nr圈省略列混合变换外,每圈均包含字节代替变换、行移位变换、列混合变换和圈密钥加法四层,第Nr圈迭代后的结果仍是一个状态矩阵(4×4的字节矩阵),将其恢复成状态即为密文(输出状态)。

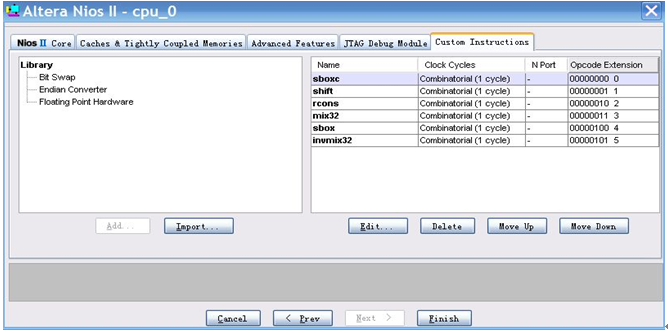

经过分析,AES算法中耗时比较多的模块包括字节代替变换、列混合变换、循环移位和密钥扩展算法中的圈常数生成模块。本设计采用自定义指令的方式实现上述各个模块。

宏“ALT_CI_SBOXC”定义为字节代替变换,其功能是完成32bit数据的S盒查找,输出为32bit的查找结果。

宏“ALT_CI_SHIFT”定义为移位指令,其功能是对输入的32bit数据进行左循环移位,移位长度为一个字节。

宏“ALT_CI_RCONS”定义为圈常数生成指令,其功能是对不同的输入选择不同的32bit圈常数进行输出。

宏“ALT_CI_MIX32”定义为列混合变换,其功能是对输入的32bit数据进行混合变换,输出为32bit的混合结果。

宏“ALT_CI_INVMIX32”定义为逆列混合变换,其功能是对输入的32bit数据进行逆混合变换,输出为32bit的混合结果。

宏“ALT_CI_SBOX”定义为逆字节代替变换,其功能是完成32bit数据的逆字节变换。

AES算法自定义指令如下所示。

下面是完成AES一轮加密所使用的核心自定义指令程序代码。

alt_u32 ming0,ming1,ming2,ming3; //初始明文

alt_u32 key0,key1,key2,key3; //初始密钥

alt_u32 temp0,temp1,temp2,temp3,m[4], t[4],n[4]; //中间变量

//密钥扩展算法

{

alt_u32 tempa,tempb,tempc,tempd;

tempa=k[j-1][3];

tempb=ALT_CI_SHIFT(tempa); //循环左移一个字节

tempb=ALT_CI_SBOX(tempb); //S盒代替

tempc=ALT_CI_RCONS(j-1); //圈常数生成

tempd=tempb^tempc;

}

//字节代替实现

m[0]=ALT_CI_SBOX(temp0);

m[1]=ALT_CI_SBOX(temp1);

m[2]=ALT_CI_SBOX(temp2);

m[3]=ALT_CI_SBOX(temp3);

//列混合实现

t[0]=ALT_CI_MIX32(n[0]);

t[1]=ALT_CI_MIX32(n[1]);

t[2]=ALT_CI_MIX32(n[2]);

t[3]=ALT_CI_MIX32(n[3]);

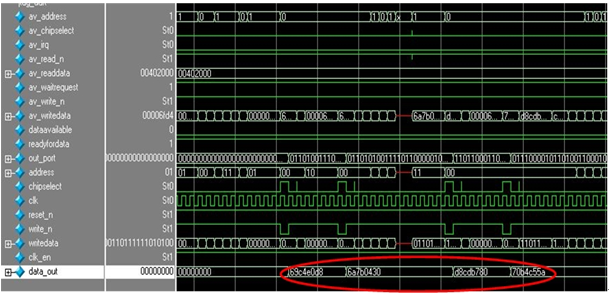

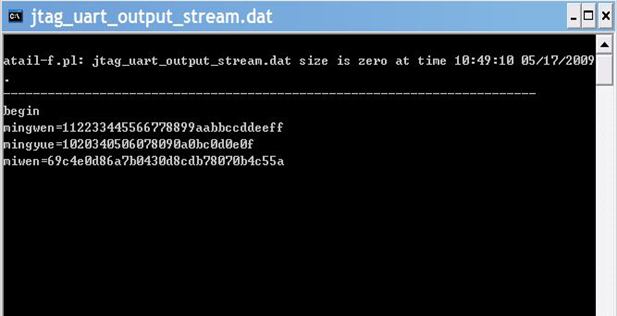

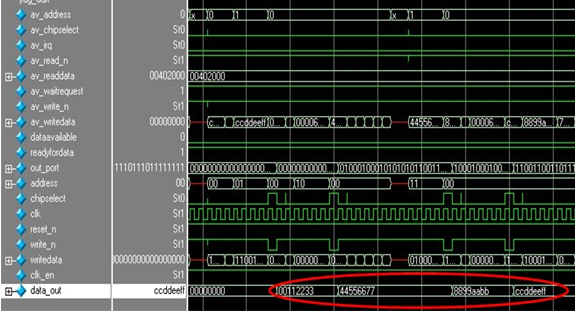

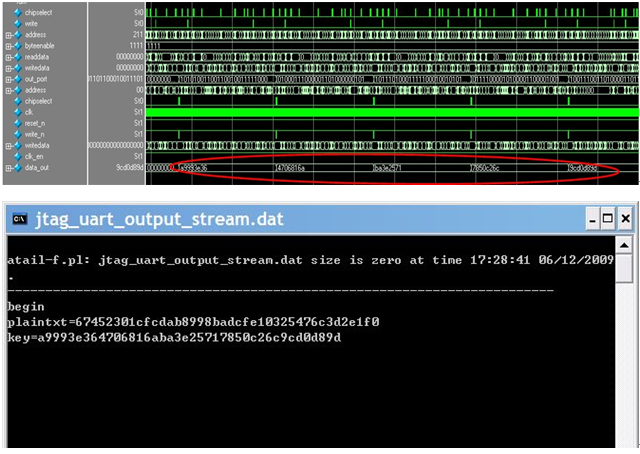

采用自定义指令的方式实现AES算法,并通过Modelsim进行仿真。仿真结果如下所示:

采用的测试向量是:

明文{ming0,ming1,ming2,ming3}=0x00112233445566778899aabbccddeeff;

密钥{key0,key1,key2,key3}=0x000102030405060708090a0b0c0d0e0f;

加密结果如图中红圈标注所示: 69c4e0d8,6a7b0430,d8cdb780,70b4c55a

AES解密是加密的逆过程,我们采用与加密相同的方法进行AES算法解密的设计,并用Modelsim进行功能仿真,实验结果如图所示。

5.3.2 SHA-1杂凑算法设计与实现

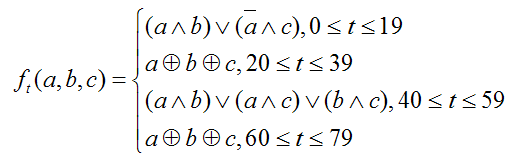

安全哈希标准(SECURE HASH STANDARD,SHA-1)是由美国国家标准技术研究所和美国国家安全局共同设计的杂凑算法,是使用最为广泛的安全杂凑算法之一。SHA-1算法接受任意长度的输入数据,输出160比特的散列函数值。将要处理的消息首先进行初始化处理,使得消息的比特长度是512的整数倍。具体做法是在要处理的消息x的二进制表示之后先填入一个1,然后再填加若干个0,使得消息的比特长度是512的整数倍少64比特,最后在最低的64比特位填入消息x的比特长度的二进制表示。

整个算法使用了3类,80个函数,具体如下所示:

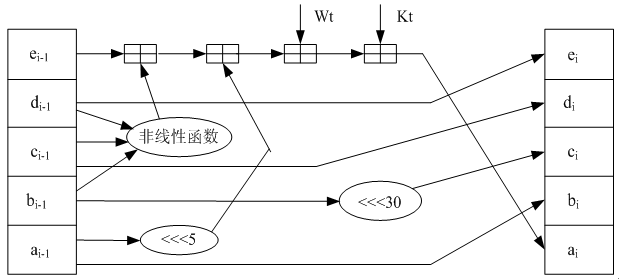

下图给出了SHA-1算法一次运算过程:

SHA-1伪代码描述如下所示。

表4 SHA-1算法描述

INPUT: H0,H1,H2,H3,H4

OUTPUT: H0║H1║H2║H3║H4

For i←1 to n

令Mi=W1║W2║…║W15,其中每个Wi是一个字

For t←16 to 79

Wt←ROTL1(Wt-3⊕Wt-8⊕Wt-14⊕Wt-16)

End for

A←H0

B←H1

C←H2

D←H3

E←H4

For t←0 to 79

temp←ROTL5(A)+ft(B,C,D)+E+Wt+Kt

E←D

D←C

C←ROTL30(A)

B←A

A←temp

End for

H0←H0+A

H1←H1+B

H2←H2+C

H3←H3+D

H4←H4+E

End for

根据SHA-1算法组成,我们自定义了两条指令,分别为:

宏“ALT_CI_CLA_32”定义为加法指令,完成模232加法;

宏“ALT_CI_SHIFT”定义为循环左移指令,完成可重构移位操作。

SHA-1算法中自定义指令如下所示。

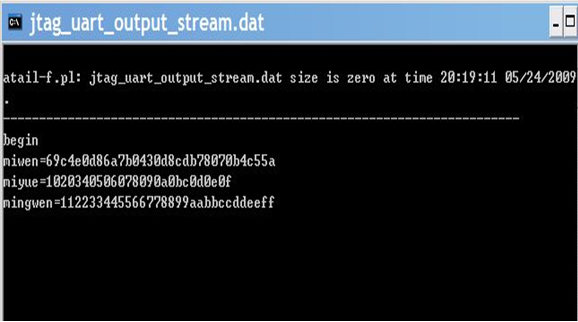

采用自定义指令的方式实现SHA-1算法,并通过Modelsim进行仿真。仿真结果如下所示:

采用的测试向量是:

消息plaintxt= 0x67452301cfcdab8998badcfe10325476c3d2e1f0;

杂凑结果如图中红圈标注: a9993e36,4706816a,ba3e2571,7850c26c,0x9cd0d89d;

5.4 USB控制器

本设计中ISP1362作为主、从设备控制器,提供各种操作的控制信号,包括 RD、WR、DRQ、DACK、ADDR及CS等,实现主机与安全数码伴侣、U盘与数码伴侣通过USB接口的通信。ISP1362接口控制器设计主要包括读时序发生器、写时序发生器及DMA时序发生器。

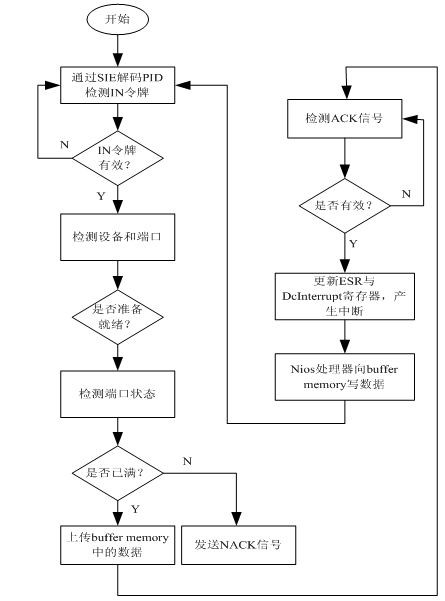

5.4.1 DC数据传输协议

1.输入数据传输协议

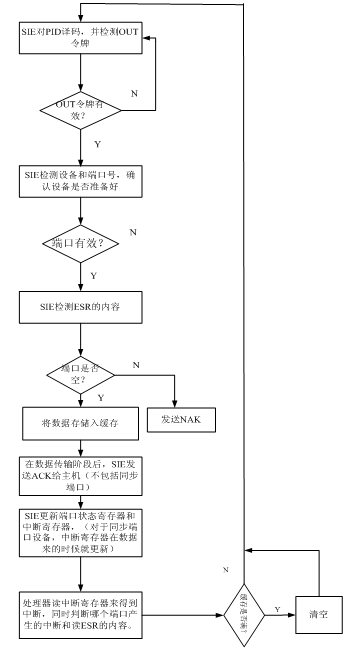

(1)通过Serial Interface Engine (SIE)解码Packet ATAntifier (PID)检测IN令牌的到来。

(2)检测设备号和端点号确认是否准备就绪。

(3)如果端点有效,SIE检测DcEndpointStatus register (ESR)的内容。如果端点已满,则发送buffer memory中的数据,否则发送NAK握手信号。

(4)SIE检测是否收到主机的ACK信号。如果收到ACK信号,则SIE更新ESR和DcInterrupt寄存器的内容,并向NiosII处理器发送中断信号。

(5)收到中断信号后,NiosII处理器读DcInterrupt寄存器判断中断的来源和ESR的状态。如果buffer memory为空,则处理器填充新的数据,等待下一个IN令牌的到来。其流程图如图所示。

2.输出数据传输协议

下图为输出数据流程

5.5.2 DC读写时序

1.DC读时序

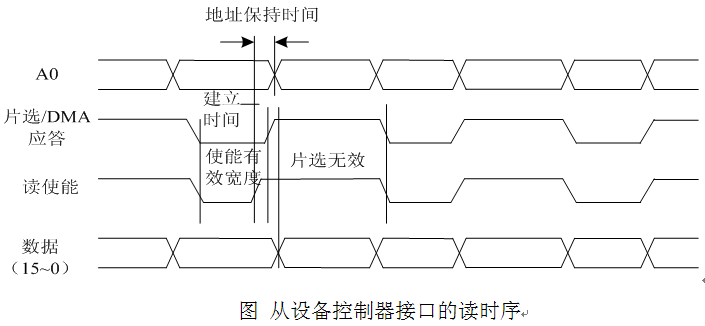

从设备控制器接口的读时序如图所示。

检测地址线A0是否为低,如果为低则判断片选/DMA应答的状态。片选信号和读使能同时为低时,从数据端口读入16位数据。片选信号为高,DMA应答信号和读使能信号同时为低时,启用DMA方式读数据。

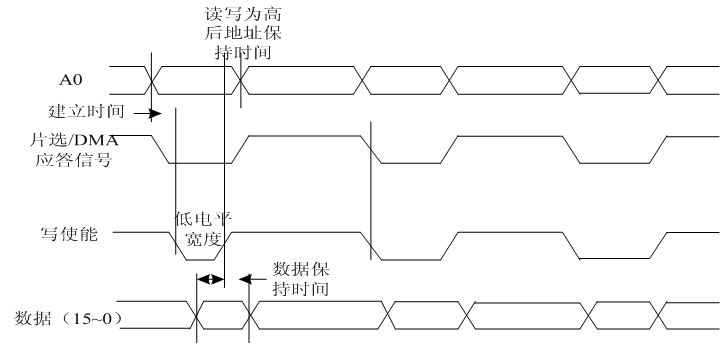

2.DC写时序

检测地址线A0是否为低,如果为低则判断片选/DMA应答信号的状态。片选信号和写使能信号同时为低时,从数据端口写入16位数据。片选信号为高,DMA应答信号和写使能信号同时为低时,启用DMA方式写数据。

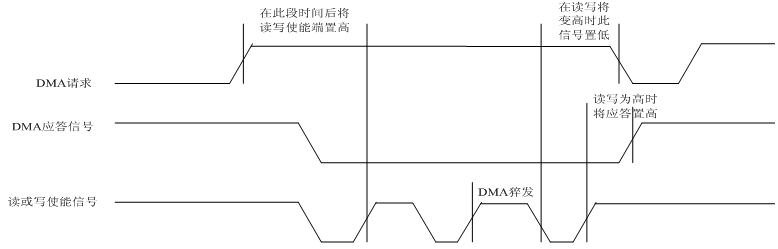

3.DMA突发传输模式时序

DMA突发传输模式时序如下所示。

5.6扩展接口电路设计

基于DE1的外设扩展接口,我们设计了DE1板与LTM、硬盘间的接口电路。本设计中DE1板子作为主控制器,控制硬盘数据的写入和读出。具体电路如下所示。

5.7 指纹识别器

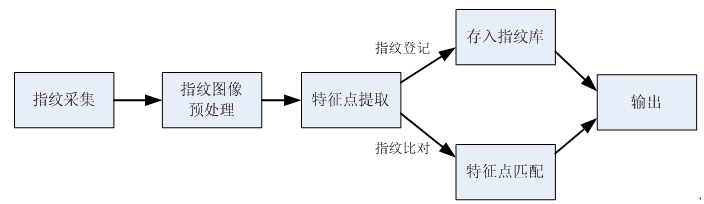

指纹识别器控制模块由指纹采集设备和NiosII处理器两部分组成。根据本设计的要求,从产品的性能、成本、接口等多方面综合考虑,我们最终选用杭州中正公司的SM-620K指纹识别器作为指纹采集设备。指纹识别的基本原理如图所示。

SM-620K指纹识别器采用光学指纹传感器进行指纹数据采集,由DSP处理器和FLASH等芯片构成,具有指纹图像处理、模板提取、指纹搜索和模板存储等多项功能。该识别器外接口为标准的RS-232串口,可以直接与DE1开发板相接。识别器的工作模式分为独立模式与命令模式。在本设计中,我们采用命令模式,通过NiosII处理器发送一系列组合指令,实现指纹登陆、指纹识别和密钥生成等三个过程,从而完成该模块的各项功能。

5.7.1 用户指纹初始录入

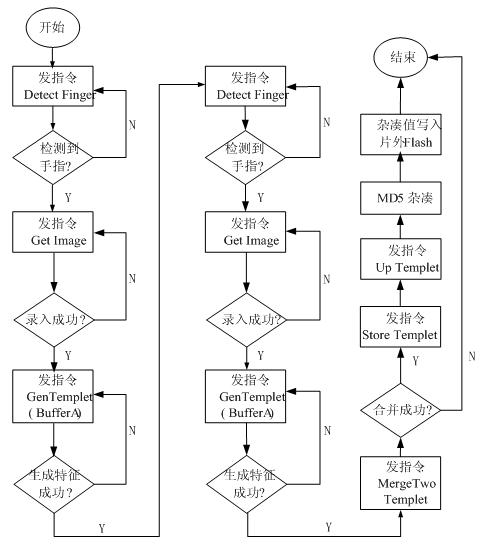

指纹登陆过程如下所示。

当安全数码伴侣增加新用户时,需要对新用户的指纹进行初始录入,将其指纹信息存入系统指纹库。在初始录入过程(流程如上图)中,NiosII处理器通过串口向指纹识别器发送以下指令:

初始化之后,NiosII处理器不断发送指令Detect Finger用来检测光学传感器上是否有手指。若得到肯定应答,发送指令Get Image录入该指纹图像到指纹识别器的图像缓冲区;如若没有检测到用户手指信息,则继续循环发送该指令。

在检测到有用户录入指纹后,发送指令Gen Templet(Buffer A)对录入的图像进行特征提取,得到的特征数据暂时存放于模块缓冲区A中,第二组采集到的特征数据放于缓冲区B中。为了得到最能体现指纹特征的一组数据,NiosII处理器发送指令Merge Two Templet对获得的两组特征数据进行合并,作为该枚指纹的模板暂时放于缓冲区内,并向NiosII处理器返回状态信号。若合并不成功,则本次登陆以失败结束;若合并成功,发送指令Store Templet将指纹的模板文件存储于指纹识别器的Flash指纹库中,并为其分配唯一存储序列号UserID,为以后指纹匹配提供依据。在发送指令Up Templet后,对接收到的指纹模板进行SHA-1杂凑,最后将杂凑值写入片外Flash,为系统用户提供工作的主密钥。

5.7.2 用户指纹比对过程

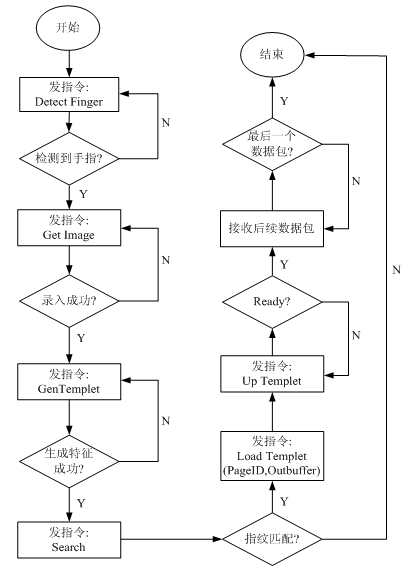

指纹匹配过程如下图所示。

安全数码伴侣开机时,如果用户要使用安全功能,需要进行指纹登录,系统将用户指纹与指纹库中已录入的指纹进行匹配,匹配通过则指纹登录成功,此时指纹识别器上传用户唯一的ID。CPU_I在收到用户的ID后就从片外Flash中搜索相对应的杂凑值,作为系统工作的主密钥。指纹匹配流程如上图所示,NiosII处理器通过指纹识别模块的光学传感器,录入要识别的指纹图像,对录入的图像处理后提取特征,再发送Search指令将该特征数据与指纹库中的指纹模板进行模糊匹配比较。若匹配通过,可得到该用户的UserID,NiosII处理器发送指令Up UserID,然后根据UserID将片外Flash中的指纹杂凑值写入NiosII处理器的存储区域,这样就完成了一次指纹匹配过程。

下图为NiosII初始化之后通过串口向指纹识别器发送“检测手指”的仿真时序图。(Detect Finger命令包为:01H,00H,00H,00H,00H,00H,01H,00H,03H)

5.8系统软件设计

5.8.1 嵌入式操作系统μC/OS

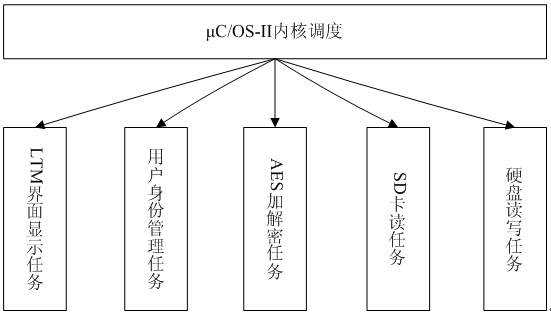

安全数码伴侣要实现SD卡文件浏览、文件加解密、用户身份认证、用户管理、用户图形操作界面等多项功能,系统控制复杂,需要使用实时操作系统(RTOS)来对系统的各种功能进行管理。

系统中运行的主要任务包括:LTM界面显示任务、数据加解密任务、SD卡读任务、硬盘读写任务、用户身份管理任务。系统运行时不同任务有不同的优先级,供操作系统进行调度。这些任务交互作用,共同完成对数码伴侣的控制功能。

系统任务调度示意图如下所示。

5.8.2 图形用户界面μC/GUI

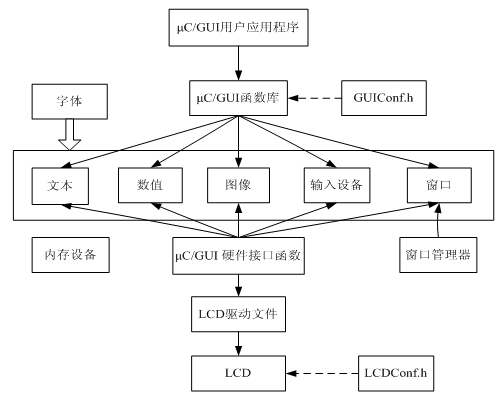

1.μC/GUI的体系结构

μC/GUI的软件体系结构如图38所示, C/GUI函数库为用户程序提供GUI接口,包含的函数有文本、数值、二维图形、输入设备以及各种窗口对象。在本设计中输入设备是触摸屏;二维图形包括图片、直线、圆等;窗口对象包括按钮、编辑框、进度条等。可以在GUIConf.h文件中对μC/GUI的函数库进行配置,如是否采用内存设备,是否采用窗口管理器,是否支持操作系统、触摸屏、以及动态内在的大小等。与硬件有关的各种属性在文件LCDConf.h中进行配置,如液晶屏的大小、颜色以及液晶接口函数等。

μC/GUI的软件体系结构如下图所示。

2.μC/GUI的移植

μC/GUI提供了源代码,可以方便地移植到系统平台下。具体过程如下:

(1)在LCD.h中定义数据类型,使其与Nios II 中的数据类型相吻合;

(2)修改LCDConf.h文件,定义LCD的大小、颜色、像素等。

#define LCD_XSIZE (800) /* 水平分辨率为800 */

#define LCD_YSIZE (480) /*垂直分辨率为400 */

#define LCD_BITSPERPIXEL (24) /*每像素24位 */

此外按照μC/GUI规定,定义与底层硬件相关的4个读写函数:LCD_READ_MEM()、LCD_WRITE_MEM()、LCD_READ_REG()、LCD_WRITE_REG()、然后定义控制器初始化函数LCD_INIT_CONTROLLER()。

(3)修改GUIConf.h文件。

#define GUI_OS (1) /* 支持嵌入式操作系统 */

#define GUI_SUPPORT_TOUCH (1) /* 支持触摸屏*/

#define GUI_SUPPORT_UNICODE (1) /* 支持unicode字符串*/

#define GUI_DEFAULT_FONT &GUI_Font6x8 /*默认字体*/

#define GUI_ALLOC_SIZE 12500 /*分配的动态内存*/

(4)μC/GUI与lcd驱动函数的连接,主要修改LCDWin.c文件;

(5)修改GUITouchConf.h文件,对触摸屏进行配置。

编写以下四个函数:

TOUCH_X_ActivateX():测量X轴数据

TOUCH_X_ActivateY():测量Y轴数据

TOUCH_X_MeasureX():根据AD转换结果返回X的值

TOUCH_X_MeasureY():根据AD转换结果返回Y的值

(6)μC/GUI与操作系统的整合,主要修改GUI_X.c文件。

设计中采用了嵌入式操作系统μC/OS-II,还应该改写与操作系统的接口函数。系统时间函数:GUI_X_GetTime()、GUI_X_Delay(),以及任务调度函数: GUI_X_Unlock()、GUI_X_Lock、GUI_X_GetTaskId()、GUI_X_WaitEvent()、GUI_X_InitOS()。

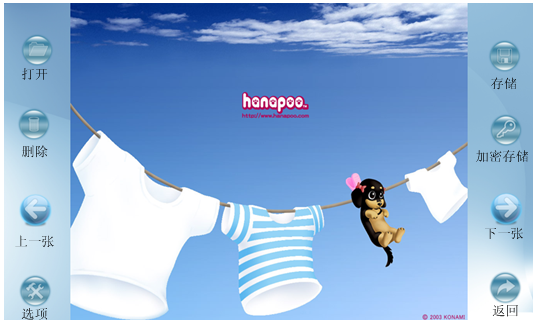

3.μC/GUI的验证

根据以上步骤,移植μC/GUI到Nios II处理器,对μC/GUI进行初步验证。该验证在LTM上显示图片,并能将当前浏览的图片以PIO或DMA的方式写入硬盘。设计界面如下图所示。

(Revision: 2 / 2009-09-14 17:28:19)

6. 设计特点 (Preliminary Paper)

1.嵌入式实时操作系统(RTOS)嵌入式实时操作系统是本设计中各个模块有序运行的重要保证。本作品从系统角度出发,将图片的浏览、图片的加解密、图片的移动及图片的显示等多种功能集成在一个系统中,通过操作系统提供的μC/GUI 图形用户界面,有序完成多任务调度,最终实现安全数码伴侣的多种功能。2.双核NiosII处理器结构在FPGA内部实现了两个(主、从)NiosII软核处理器,两者通过共享SDRAM进行通信。这种设计充分利用了双核协同工作的优势,各个CPU分别承担不同的功能,便于控制和协调,能够有效改善CPU的性能。不仅完成了外部指纹识别器的控制,同时支持多用户对SD卡和硬盘中存储图片的浏览和移动,并能够有选择地进行加解密操作,降低了系统设计的成本。3.用户自定义指令实现关键算法模块由于AES算法与SHA-1杂凑算法均是复杂的数据运算过程,用软件实现的方式必定会降低系统的速度,本设计利用Altera公司提供的SOPC Builder添加了自定义的用户指令,将复杂度较高、耗时较多的模块在硬件中实现,可以大大提高数据的处理速度,保证了数据交互的实时性。在设计中采用硬件描述语言实现了AES加解密与SHA-1杂凑算法中的关键模块,进行了硬件加速,使系统的整体性能得到了大幅度的改善。4.硬盘接口支持多模式数据传输本作品设计了支持硬盘ATA接口读写时序发生器,能够支持PIO的五种模式与DMA的三种模式。在开发板与硬盘的交互过程中,能够根据数据传输速率的要求自适应的启动相应的读写发生器,满足了现实中应用的需求,丰富了系统的功能。5.可靠的用户身份认证本设计通过对用户的指纹信息进行杂凑运算,使得每个用户只需在指纹识别器上轻轻一按,系统就能够自动完成对用户身份的认证,同时根据不同的用户,采取不同的密钥生成方案,产生合法用户唯一的加密密钥,提高了整个系统的安全性。6.自主开发用户图形界面本设计利用友晶公司开发的LTM模块,基于μC/GUI自主设计开发了支持安全数码伴侣所有操作的图形界面,省略了按键操作。用户只要轻轻一点,系统即可按需完成所有安全功能,并及时地将操作完成信息显示在LTM上,操作更加简捷、高效。7.自主开发的多功能接口扩展板由于DE1开发板具有的丰富外设扩展接口,利用两个40针的扩展口,不但自行开发了与硬盘ATA接口相匹配的接口转换板,而且通过管脚的分时复用,实现了DE1开发板与LTM、USB设备及主机的连接,拓宽了产品的使用空间。8.产品的上市时间短本作品的升级与开发空间大,考虑到现实应用中的情况,对数据加解密的算法很多,本作品选取的是AES密码算法,但是由于本作品采用的是NiosII自定义指令方式,依托与NiosII处理器灵活的可编程性,针对不同的用户可以轻松的在NiosII中更改其它的密码算法,可以在很短的时间内就可以开发出新的产品,缩短了产品的更新与升级时间。整个设计过程贯穿了Altera公司NiosII 处理器灵活的设计方法和SOPC领先的设计理念,给设计人员带来了极大的方便,同时FPGA摒弃了传统的思想——设计更改必须更改硬件,实现了处理器与硬件逻辑的无缝接口,保证了系统的稳定性,缩短了产品的开发周期。(Draft / 2009-06-15 19:11:55)

7. 总结 (Final Project Paper)

很荣幸能够进入亚洲创新设计大赛地复赛阶段,短短两个月地时间,对我们设计小组来讲是一段不断学习,不断实践地经历。我们感受到QuartusII设计功能地强大与灵活。在SOPC Builder中,系统为我们提供了很多常见地IP核,这使我们地工作变得更加轻松和方便,我们也可以加入自己定制的IP核以及自定义指令,满足用户特定的要求,这使我们的设计工作变得更加灵活。特别是自定义指令,现在增加到256条,足够满足用户得要求。在软件开发方面,QuartusII又集成了Nios IDE。我们可以在NIOS IDE图形界面中完成从程序设计到最后下载运行的全过程。特别是CycloneII架构的FPGA给我们的开发提供了强有力的支撑。

1、 成本优化的新型可编程架构

CycloneII低成本架构通过仔细选择封装形式来提供足够的I/O管脚和功耗特性,通过提高产品设计工艺的效率来进一步减少裸片的尺寸。以此为基础,CycloneII系列器件具有可与ASIC竞争的成本优势、丰富的逻辑资源和存储资源、时钟管理电路和高性能I/O资源。

2、 FPGA上的低成本DSP实现

CycloneII器件中的M4K块能够用于实现软乘法器,从而支持图像处理、音频处理和消费类电子系统等多种高性能、低成本的DSP应用。

3、 外部存储器接口

CycloneII器件提供了专用的外部存储器接口电路,用于与双数据速率(DDR)SDRAM、FCRAM以及单数据速率(SDR)SDRAM器件进行快速、可靠的数据交换,最高速率可达到266Mb/s。

4、 支持广泛的接口和协议

CycloneII 器件支持多种串行总线和网络接口,还支持广泛的通信协议。Altera公司为这些应用提供了一系列已专门针对CycloneII器件结构优化的IP。

5、 内含增强型锁相环

CycloneII 器件内置至多两个增强型的锁相环,可用于简化板级设计的时序问题,以及为大批量价格敏感性应用提供高性价比的时序控制方案。

6、 先进的I/O支持

CycloneII 器件支持最多129个通道的LVDS、RSDS等差分I/O标准,以及LVTTL、LVCOMS、SSTL-2、SSTL-3、PCI等单端I/O标准,以便与电路板上的其他芯片通信。

7、 NIOSII 嵌入式处理器

NIOSII 系列处理器以非常成功的一代NIOS处理器为基础,提供高性能内核、低成本内核和性价比平衡的标准内核等三种内核供设计者选择。

我们深刻体会到FPGA以及软核设计方式的优点,特别是在进行产品开发时,采用FPGA以及软核设计方式可以缩短开发周期,减少开发风险,提前抢占市场。

(Draft / 2009-09-14 17:29:01)