Profile - CN497

CN497

基于SOPC技术的“个人电子实验室”

吉林大学电子科学与工程学院 电子信息工程

Project

Name of Project: 基于SOPC技术的“个人电子实验室”

Contact Information

Name: 代寿刚 E-Mail: xiaogang0619@mails.jlu.edu.cn Telephone: 043185163754 Mobile Phone: 13610789860 Mailing Address: 吉林大学前卫南区南苑一舍352寝

Contest Advisor

Name: 杨罕 E-Mail: yanghan@jlu.edu.cn Telephone: 13089111878

Members

No. Name English Name 1 代寿刚 xiaogang0619@mails.jlu.edu.cn Dai Shougang 2 陈宇 871888386@163.com Chen Yu 3 杨文浩 calmreader@163.com Yang Wenhao

Project Paper - view as Preliminary(2009/06/15), Final(2009/09/14), Draft, Latest

1. 设计概述 (Preliminary Paper)

一、选题背景:

- 每一个真正的电子人,都希望拥有一套完备的电子仪器的集合。她不仅具有示波器、频谱分析仪、数字滤波器、信号发生器、逻辑分析仪、频率计、数字万用表等等仪器的功能,还能进行仪器间的实时通信,能够将测试数据上传至个人PC机,这样就可以直接使用科学绘图工具,数据处理软件处理测试数据,规范的完成实验报告,科技论文的撰写,使学生轻松愉快地进行电子电路的学习和设计。

- 注意到市场上的常用仪器都性能卓越,但是它们的价格往往比较昂贵。我们(特别是学生)在做常见的电子电工实验时,往往用不到仪器性能的上限,而更多的要求仪器有较多的功能(比如AD实验希望既能显示模拟端的波形也能进行数字端的逻辑分析)。

- 虚拟仪器也许能满足以上的要求,但是虚拟仪器一但出厂之后功能就固定了,系统不容易升级。况且,虚拟仪器需要依赖上位机进行大量高速数据的处理,这就要求它使用PCI等等高速总线与上位机进行通信。这样做不仅成本较高,而且在一定程度上影响了上位机的正常工作。

- 学校的硬件设施有限,往往不能满足每一位电子类学生的实践动手的要求。如果学生们能够拥有一套低成本、多功能的实验仪器集合,他们就能随时地通过实践动手提高自己的能力,并最终与就业市场无缝接轨。

二、系统简介:

- 本项目以电子工程师和电子类学生的实际需求作为出发点,设计一款基于SOPC技术,以Altera公司的DE系列开发板作为硬件平台,集多种功能模块为一体的低成本、可升级的“个人电子实验室”(Personal Electronics Laboratory,PEL)。

三、适用范围

- 学生群体:由于接入系统的模块可任意更换,我们可以选择成本最低、性能最适合的版本应用到电子类的学生当中。这样学生在寝室便可以根据我们提供的引导设计视频文件,进行常见的电子电工实验。

- 电子工程师:工程师们可以选择性能较高端的软件配置系统(如NiosII-f)和硬件子模块接入系统进行常见的工程测试,这特别适合他们进行现场调试的场合。

- 学校实验室:我们也可以在系统里面接入用于无线通信的子模块,让每一台“个人电子实验室”可以相互通信。这样,当老师在引导学生进行实验的时候,学生们可以在自己的座位上真实地复现老师演示的实验过程。

四、选用本款Altera器件的原因

- 系统中的许多模块(比如示波器模块、逻辑分析模块)要求处理器具有高速数据处理的能力,而这恰好是以Altera公司的FPGA器件作为硬件平台而构成的SOPC系统的优势所在,而这也使PC机得以从容地显示相应的信息而不必再奔命于庞大的数据处理。

- 作为仪器类项目,“个人电子实验室”对速度和精度的要求较高。而利用NiosII中的自定义指令与C to H加速器,我们可以在不影响系统工作的前提下进行硬件的加速,使FPGA得以避开硬件级的大量的重复性工作而专注于大量高速数据的处理中,从而进一步提高系统的性能。

- SOPC技术的可重构性很好的解决了系统可扩展的要求,我们可以因地制宜地使用NiosII/e、NiosII/s、NiosII/f三种系统,分别满足不同的人群的需要。利用系统的可随时更新的能力,我们还能设计软件并接入自定义模块进行其它有趣的实验,比如利用TC35模块的语音通话功能的实时性,设计FPGA的音频解析和加密子模块,使系统能够进行超远距离无线控制的实验。

- Qaurtus II提供丰富的IP核。这样,我们可以方便的定制FIR和IIR并灵活地设置其参数,实现数字滤波器子模块。

- NiosII软处理器的Avalon构架为我们的设备管理提供了无可比拟的方便。Avalon总线构架中,所有外设的接口与avalon总线时钟同步,不需要复杂的握手/应答机制;地址线与数据线使用分离的、专用的端口,外设不需要识别地址总线周期和数据总线同期:这使得我们可以任意扩充满足接口协议的子模块,这样系统也可以轻松地进行升级。

- 另外,DE2开发板上的各种资源也比较适合系统各种功能的实现:

- 512KB的SRAM可以用作示波器等仪器的高速FIFO;

- 8MB的SDRAM可以用作VGA显示彩色界面的缓存;

- IDE接口作为各种子模块的物理总线接口;

- USB从端口或是UART接口可用于与上位机进行实时通信;

- 16*02液晶显示模块和数码管模块可以用来显示系统的各种工作状态以及测得的电压等实时数据;

- VGA接口可用于接入VGA来显示各种波形、参数以及人机界面;

- SD卡可用来实现存储各种波形和数据的功能;

- PS2接口或者USB主端口使系统可以接入鼠标进行系统操作等等。

综上,我们选择了本Altera器件作为“个人电子实验室”的设计载体。

(Revision: 16 / 2009-09-14 22:11:42)

2. 功能描述 (Final Project Paper)

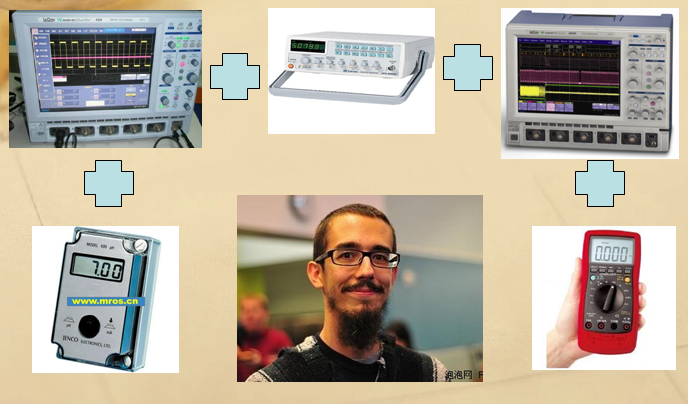

图——2.1

“个人电子实验室”(PEL)是一种集示波器、信号发生器、逻辑分析仪、频谱分析仪、数字滤波器、频率计等等仪器于一体,以FPGA作为高速的数据处理核心,并利用NiosII软处理器来管理各种外部设备的综合型仪器,如图2.1所示。她可以帮助电子类学生轻松地完成各种综合性实验,也可以帮助电子工程师们进行常见的工程测试和各种场合的现场调试,成为他们的好帮手,具有广阔的应用前景。

以下是PEL的功能简述:

- 示波器功能:FPGA通过控制高速AD的采样速率,将模拟信号转换成数字信号并缓存在FPGA内部的FIFO里,在给予参数分析、比例变换等处理后使用VGA或上位机进行显示。我们使用了NiosII的自定义指令对输入波形的均值、功率、平方根等等数据进迅速计算、显示,用硬件逻辑电路实现系统中软件处理耗时多的关键算法,提高了系统的效率,并最终实现了示波器的AUTOSET功能。

- 频谱分析仪:与示波器相似,FPGA首先对高速AD采样得到的数据进行缓存,然后对原始数据进行FFT变换,并在对频率、相位等等参数进行计算分析后,最终使用VGA或上位机进行时域、频域的波形和参数的显示。频谱分析仪中,需要调用C语言的FFT变换函数,运算量相对较大。我们使用C2H对FFT子函数进行硬件加速,大大提高了程序的运行效率,使频域的波形与参数得以流畅地显示。

- 频率计:将待测信号通过DE2的EXT_CLK端口输入到频率计子模块中,计算得到信号的频率值。我们利用FPGA高速、稳定的特点,在频率计自定义模块中使用纯硬件完成频率的测量过程,并且达到了较高的精度。NiosII只需要实时读取模块中的频率值并进行显示即可。整个测量延迟为0.2秒。

- 信号发生器:根据直接数字频率合成(DDS)原理,将正弦的波形数据存储在FPGA内部的ROM中,通过控制ROM的寻址速度便可以实现频率的控制,最终将数据输出到高速DA进行转换,同时通过相应的波形变换电路便可得到常用的正弦波,三角波,方波等波形。

- 数字滤波器:仪器输入部分的原理与示波器相似,而输出部分的原理与信号发生器的原理类似。我们使用DSP中的FIR或IIR算法对输入信号进行数字滤波处理,并将处理后的信号通过高速DA电路输出。为了方便演示,我们只制作了低通滤波器模块,当输入信号频率达到滤波器的截止频率时,滤波器的输出波形得到明显的衰减,输入信号超过截止频率时,波形被截止。

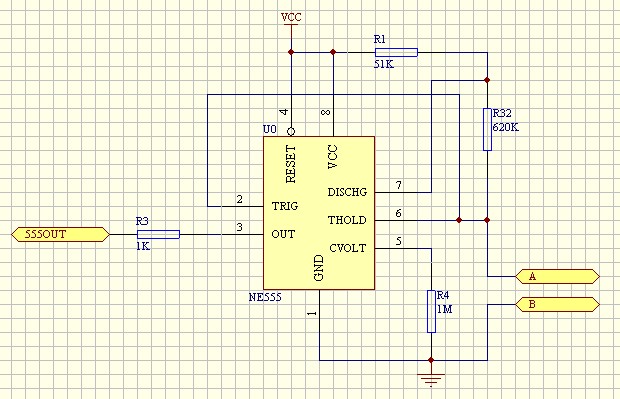

- 数字万用表功能:作为样机,我们自制了电压和电容的测量电路,实现对电压与电容的测量。电压的测量采用一个12位的高精度AD转换器实现模拟到数字的转换,电容的测量则使用一个NE555芯片构成单稳态电路,从而将电容的测量转变为频率的测量,提高了测量精度。

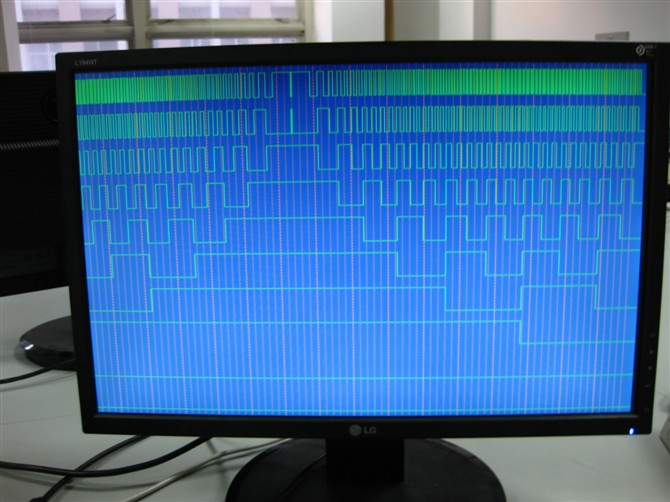

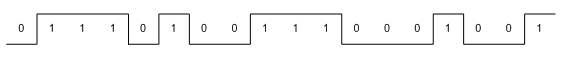

- 逻辑分析仪:我们使用纯Verilog语言编写了逻辑分析仪核心模块,其中包括信号采集触发模块、双口RAM模块、采样频率控制模块和显示模块。本模块能实现10路逻辑电平的捕捉,并显示于VGA接口的显示器,具有较高的实用性。

- 上位机操控:利用LabView在上位机开发整个系统的虚拟控制平台,实现了PC机对PEL的宏观操控;开发了电子设计动态演示教程,使学生能结合PEL实现电子设计的自主学习与创新实验。

正是有了FPGA速度快、功耗低、可靠性高,以及它的强大的数据处理能力与时序控制能力等等优势,才使我们整个系统的设计具有了可行性,才使PEL所有的功能有了实现的可能。

(Revision: 29 / 2009-09-14 22:49:44)

3. 性能参数 (Final Project Paper)

一、频率计数器参数:

- 测量频率范围: 1Hz~40MHz

- 输入电压范围: 0~5V

- 测量精度: 1Hz

二、数字示波器参数:

- 输入电压范围: 0~5V

- 分辨率: 8位数据精度

- 输入信号带宽: 0~2.8MHz

- VGA分辨率: 640×480(像素)

- 最高采样速率: 40MS/s

三、信号发生器参数:

- 支持输出波形: 正弦波

- 最高输出频率: 3MHz/s

- 最高输出频率精度: 10位数据精度

- 支持输出电压幅度: 0~5V

- 支持双路: 支持

四、数字万用表参数:

- 支持测量类型: 电压、电容

- 测量电压范围: 0~5V

- 测量电阻范围: 1nF~100nF

- 测量精度: 12位数据精度

五、频谱分析仪参数:

- VGA分辨率: 640×480(像素)

六、系统电源参数:

- 直流电压: 9V

- 工作电流: 750mA

七、系统环境参数:

- 工作温度: -10~45°C

- 相对湿度: 20%~80%

八、部分器件参数:

- TLC5540: 最高采样速率40MS/s、8位数据精度

- THS5651: 最高转换速率120MS/s、8位数据精度

- LM6172: 最高转换速率160MS/s

九、系统资源利用情况:

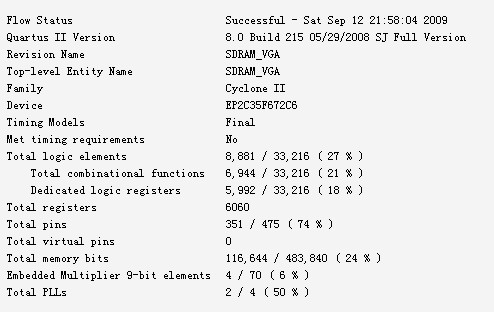

图3.1显示的是DE2开发板上EP2C35F672C6型FPGA的资源利用情况。

图——3.1

本系统的特点是外设众多,且多涉及高速的、大数据量的处理任务。所幸,DE2开发板为我们提供了强有力的硬件支持,原有的外围设备可以集成到DE2上,甚至直接放置到FPGA内部。为了完成大量重复性的数据处理,我们在系统中大量使用了自定义外设,将软件的处理任务转入底层的硬件来处理,这不仅提高了数据处理的速度,更优化了系统的性能。而NiosII软处理器的引入,我们才可以从容地管理这些复杂的外设,使得我们在这么短的时间就完成了这一项工程的开发。

说明:以上参数即是本系统的实际性能参数,我们基本实现了设计的功能与参数要求。

(Revision: 6 / 2009-09-15 00:11:46)

4. 设计结构 (Preliminary Paper)

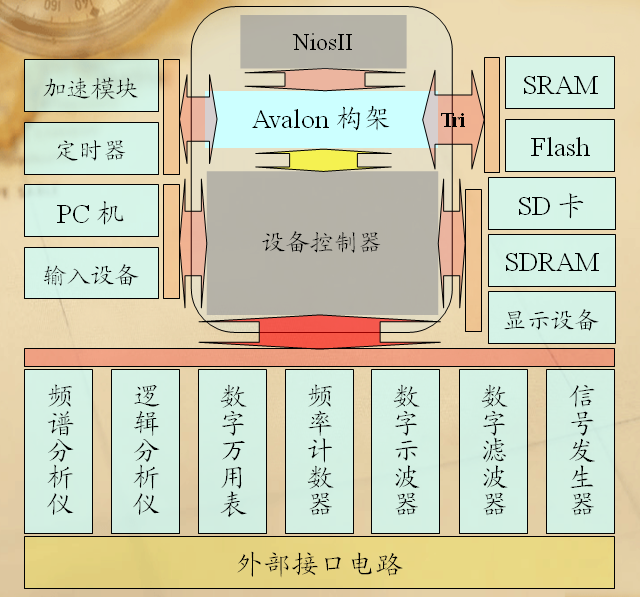

一、系统原理框图:

图——4.1

二、SOPC设计结构:

本系统的SOPC结构如图4.2所示。系统CPU采用了Nios/f结构,完成了系统数据的处理和系统外设的控制。Flash通过三态桥与Avalon总线进行通信,作为系统的复位向量存储器。SRAM则作为本系统的异常向量存储器。SDRAM作为本系统的显示缓冲存储器,通过SGDMA方式与VGA控制模块进行通信。大部分外设的控制器都挂载到了Avalon总线上,直接由CPU进行控制。利用NiosII的可重构性, 我们可以很方便的在系统里面集成各种存储器、锁相环、UART通信接口、DMA传输及自定义外设等等,这可以大大减小系统的开发周期,缩减产品的上市时间。

图——4.2

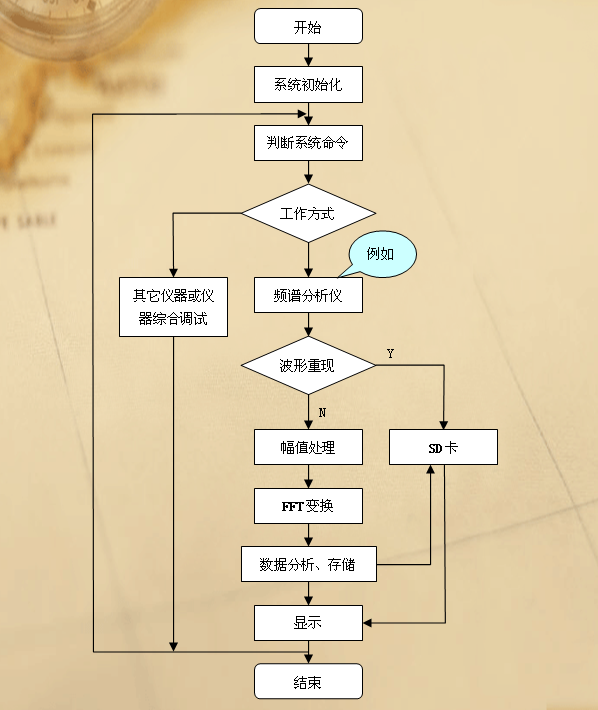

三、程序流程图:

图——4.3

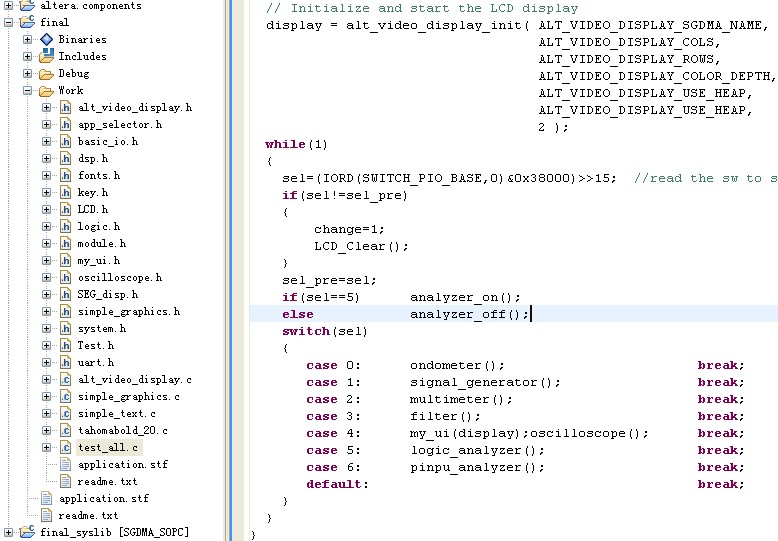

四、Nios II IDE程序设计:

图——4.4

(Revision: 12 / 2009-09-14 23:10:01)

5. 设计方法 (Final Project Paper)

“个人电子实验室”每一个模块都遵循信号的采集、数据处理、结果显示的基本流程。

一、数据采集模块

所有的模块都使用了自定义外设的方法,以SOPC组件的形式加载到Avalon总线上。

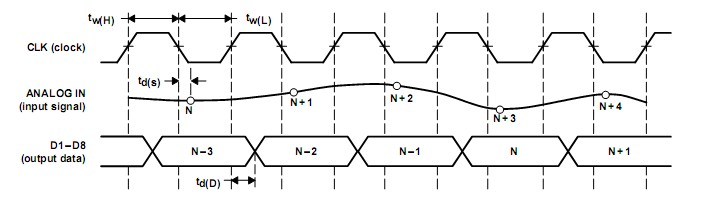

1. 本系统使用TLC5540高速AD芯片作为高速数模转换模块,控制时序如图5.1。

图——5.1

2. 系统使用MAX196作为高精度数模转换模块,实现电压的测量,其控制时序如图5.2。

图——5.2

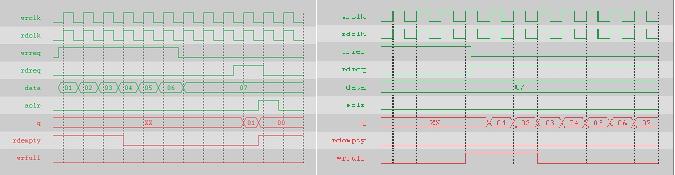

3. 并使用FPGA的On-chip FIFO作为高速的数据缓冲存储器,时序如图5.3。

图——5.3

4. 电容测量模块使用了一个震荡模块使电容的值转换为频率值,然后才进行测量,如图5.4。

图——5.4

5. 逻辑分析仪模块则直接将逻辑电平信号接入到FPGA的GPIO端口。

二、数据处理部分

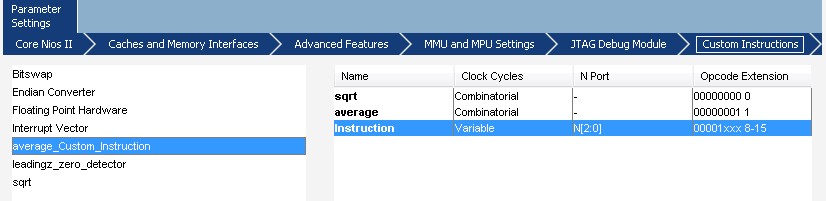

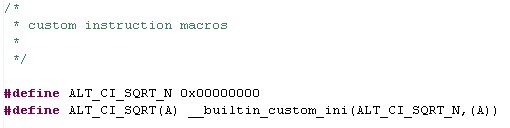

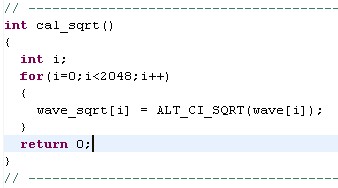

1. 使用自定义指令实现AUTOSET功能

当AD转换器写满FIFO后,CPU以极快的速度将数据读出,并控制FIFO进行下一次数据的写入。在AD将数据写满之前,CPU就必须将FIFO里面2048个数据的均值、方差、幅度、频率等等计算出来,并显示到VGA上面。如果使用纯软件来计算的话,VGA画面将每隔3秒钟左右更新一次,这显然不符合我们的设计要求。我们使用自定义指令将连加、求根等等运算硬件化,这使得运算在几十个CPU时钟里面就可以完成。实测结果也表明,画面的更新速度有了显著的提高。在此基础上,我们再利用自定义指令实现了示波器的AUTOSET功能,在读出FIFO的数据后,使用硬件快速地从2048个数据中找出两个周期的波形数据,并将其合理地显示。

图——5.5

图5.6和图5.7是自定义指令的调用情况:

图——5.6

图——5.7

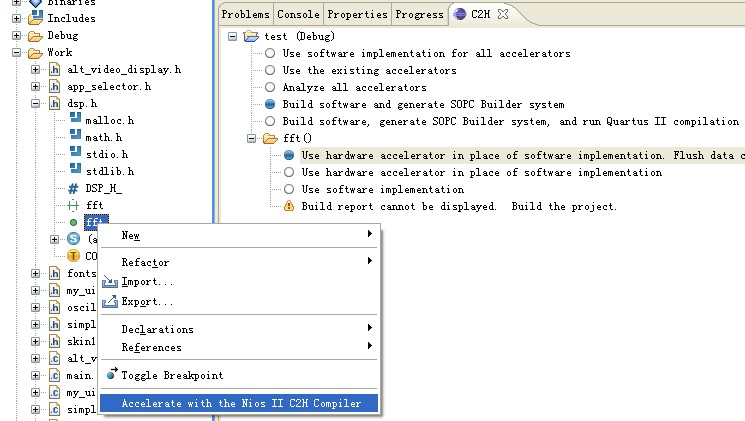

2. 使用C2H实现FFT功能

在设计频谱分析仪的时候,由于FFT涉及到大量的乘除运算,这使得VGA画面的更新速度大大降低。我们尝试过直接对FFT函数进行硬件加速,但由于FFT函数里涉及到浮点运算而不能进行硬件加速。所以我们对FFT的C语言算法进行了修改,将浮点运算转变为了整数运算,并最终使用C2H对其进行了硬件加速。通过前后对比,我们发现使用C2H能大大提高FFT的运算效率,使得画面得以极为流畅的显示,提高了系统的实时性。

图——5.8

3. 逻辑分析仪部分

3.1触发条件的控制

本设计中逻辑分析仪的采样触发条件有6种,分别为:低电平触发、高电平触发、上升沿触发、下降沿触发、边沿触发、无条件触发(立即触发)。触发条件可以通过按键控制,并显示于LCD1602上。边沿触发的程序代码如下:

always@(posedge clock)

begin

if(clken) //时钟使能信号

begin

data_r1 <= data_in;//输入数据到一级缓存

data_r2 <= data_r1;// 输入数据到二级缓存

end

end

assign s_posedge = data_r1&~data_r2;//上升沿检测

assign s_negedge = ~data_r1&data_r2; //下降沿检测

assign s_edge = data_r1^data_r2; //双边沿检测

电平触发就比较简单,只要判断读进来的值是高电平还是低电平即可,这里不再赘述。

3.2波形显示控制模块

(1)显示区域划分

设计中驱动的VGA显示器时的显示的分辨率为640×480,总共有10个通道,所以垂直部分分为10行,每行48个像素点的高度,在水平部分显示的栅格网络(用虚线显示),共分16大格,每大格再分5个小格,每小格由8个像素点组成,总共就有640个像素点。这样整个显示器的区域就划分完毕。波形显示格式如图3所示,当然屏幕背景,栅格线,波形,时间标线这几部分我们可以用不同的颜色显示,便于观看。

图——5.9 实现波形显示

(2)波形显示

图——5.10

在VGA显示驱动模块中有两个计数器,行扫描计数器hcount和场扫描计数器vcount,其输出显示有效范围分别为0-639和0-479。现以CH0通道数据分析其显示原理。行扫描计数器和双口RAM的地址是同步的,假设RAM中的数据不变,则显示区域每列读出的数据都是相同的,当场扫描计数器vcount为8时,判断D0的值,若为1输出数据显示。若为0则输出背景色或栅格;同理当vcount为40时,再次判断D0值,若为0输出数据,若为1则输出背景色或栅格。这样一来,就有高低电平波形线显示出来了,至于高电平与低电平跳变时的垂直线,我们可以在RAM数据读取出来之后再一级寄存器做个边沿检测电路,在输入与输出发生变化时,两个不同的值经过“异或”门便可输出“1”。

栅格和时间标线的显示比较简单,只要在显示区域对应的位置(比如当hcount为0、8、40时)输出栅格颜色数据就可以了,若要显示虚线,则需将vcount的值也做比较(比如vcount为奇数时显示,为偶数时不显示)。

(3)移动显示区域

本设计中RAM的存储深度取为1024,而显示器的水平分辨率为640个像素,只能显示640个波形点,但我们通过改变RAM的起始地址来达到查看所有波形数据的目的。

三、结果显示

1. 利用SG-DMA方式实现VGA彩色显示与DMA不同,SG-DMA可以在非连续的存储器和连续的地址空间进行数据传递,并且每一个SG-DMA都带有描述符序列来确定传输的数据。我们使用SG-DMA连续地读取SDRAM里面的数据,经过数据宽度变换、时钟匹配等等操作后,最终送到VGA进行显示,如图5.11所示。值得注意的是,SG-DMA控制VGA进行显示的时候,数据量相对较大,因此我们更改了SG-DMA与SDRAM之间的Arbitration,加大了数据流量,使得画面能得以流畅的显示。

图——5.11

2. 另外,DE2上集成有丰富的显示器件,我们将数字万用表测量得到的电压和电容值使用LCD进行显示,将频率计测量得到的频率值使用数码管进行显示,同时使用LED小灯显示系统的工作状态等等。

(Revision: 37 / 2009-09-15 12:36:48)

6. 设计特点 (Preliminary Paper)

一、独到之处:

- “个人电子实验室”将各种常用的实验仪器集成到一个NiosII系统里面,功能多样、全面,这非常适用于学生或者工程师们进行常见的综合实验或现场调试的场合。

- 为了提高系统的效率,我们在某些数据处理的环节采用了自定义指令的方式。这样,我们将大量重复性的数据运算转换为硬件实现,处理器可以将更多的精力用于系统设备的逻辑管理中。

- 以纯硬件方式实现了逻辑分析仪的核心模块。这极大地提高了系统运行速度与实时性。

- 对FFT进行了硬件加速。相对纯软件实现的解决方案而言,能够提供更高的帧率,使得画面显示更加流畅。

- 基于SOPC的可重构性,本系统可以方便的进行扩展与升级。

二、使用这款器件优势:

- 系统包含多种数据密集型仪器,要求处理器有强大的数据处理能力,而这正是FPGA的优势所在。利用FPGA高速的特点与它内含的DSP的强大的数据处理能力,我们可以利用硬件大大缩短数据处理的时间,使系统得以高效、稳定地运行。

- FPGA器件含有丰富的寄存器单元与逻辑单元,这为系统运行众多的子模块和处理高速、大量的数据提供了保障。

- 同时,FPGA器件具有功耗低、速度快、可靠性高的特点,这为我们在子模块性能的提升方面提供了广阔的空间。

- 最后,如前所述,开发板提供了丰富固有的硬件资源及其例程,我们可以利用这些简而实用的资源来接收用户的命令,显示各种波形、参数,标示系统的工作状态等等。

(Revision: 15 / 2009-09-14 21:04:18)

7. 总结 (Final Project Paper)

带着学习的心情,我们基本完成了整个系统的设计。

在设计过程中,我们深刻地体会到了使用FPGA进行开发的优越性。SOPC具有灵活的可重构性,正是有了这一特点,才使我们得以在这么短的时间内实现了整个系统的设计。在软件与硬件的设计对比中,我们掌握了硬件加速的使用时机与方法。FPGA可以在一定程度上将一些外部设备集成到FPGA内部(比如FIFO),这在减小系统开销的同时,更提高了系统的运行速度与可靠程度。

在这次比赛中,我们对FPGA的开发过程有了更为深刻的认识。通过充分的可行性研究、严谨的项目计划、合理的进度安排和充分的团队合作,我们不仅圆满地完成了设计要求,也深刻的体会到了团队合作的重要性。这种经历给我们每一个人都留下了一段美好的回忆和一笔宝贵的财富。

“个人电子实验室”基本实现了我们最初的设计要求,但在某些细节方面,还有待完善。在以后的学习过程中,我们将会对其性能进行完善。

最后,感谢Altera公司为我们提供了这样一个锻炼的平台!我们在学习中开阔了视野,在合作中收获了友谊。

(Revision: 6 / 2009-09-14 22:00:25)

.jpg)

.jpg)

.jpg)