Profile - CN423

CN423

基于HHT的快速瞬时频率分析仪

北京交通大学/澳门大学计算机与信息技术学院

Project

Name of Project: 基于HHT的快速瞬时频率分析仪

Contact Information

Name: 李成 E-Mail: lchapple0713@126.com Telephone: 010-51468110 Mobile Phone: 15120072881 Mailing Address: 北京市海淀区交大东路18号院学苑公寓2号楼104

Contest Advisor

Name: 丁晓明(北京交通大学)/韦孟宇(澳门大学) E-Mail: xmding@bjtu.edu.cn Telephone: 13366097763

Members

No. Name English Name 1 李成 lchapple0713@126.com li cheng 2 赵云颋 05281087@bjtu.edu.cn Zhao Yunting 3 王磊(澳门大学) wanglei.okay@gmail.com Wang Lei

Project Paper - view as Preliminary(2009/06/15), Final(2009/09/14), Draft, Latest

1. 设计概述 (Preliminary Paper)

1. 设计意图频谱分析是数字信号处理领域中的常用的分析方法。市场上也有很多种类的频谱分析仪,然而这些仪器大部分是应用FFT(快速傅里叶算法)为基准的。FFT只能描述出信号在频域的能量,不能在时域描述出信号随时间的变化。而且它们都把要分析的信号近似为线性的平稳的(现实中的信号大部分是非平稳非线性的),这势必会引出误差。

HHT(Hilbert-Huang Transform 希尔伯特-黄变换)是Nodern E. Huang在1998年提出的针对非线性非稳定信号分析的一种新颖的方法。提出后在应用方面就取得了很大的成功。该方法不同于FFT和和Wavelet(小波变换)不需要对信号有先验的假设,例如必须是线性稳定信号。通过HHT处理,可以得到信号的时间,频率,能量的3D分布图和观察信号在一时间或时间段内频率和能量分部的变化。HHT当前在国内外也只是用纯软件实现,因为HHT算法运算量很大,很少有硬件上的实时实现,2003年,美国国家航空宇航局(NASA)基于HHT算法开发了一套HHT-DPS(Hilbert-Huang Transform Fata Processing System)系统,但是该系统是基于PC机的软件实现。要想针对实时信号处理,高速的处理速度是非常必要的。

本设计正是利用HHT算法和Nios II软核处理器的硬件加速特性在Altera FPGA平台上实现一个基于时间-频率-能量三维分布的瞬时频率分析仪。现有的频谱分析仪主要在频域工作,已经无法满足对时域瞬时频率分析的要求,也局限在分析线性的平稳的信号。一台频谱分析仪动则几十万更换的成本很大,我们针对未来发展趋势利用Nios II进行大胆尝试。设计了支持串口,USB,SD卡,以太网传输的基于HHT的快速瞬时频率分析仪,很容易与现有的频谱分析设备进行通信。对现有的频谱分析仪的升级是一个低成本高回报的选择,具有广阔的市场前景。适2. 用范围及针对用户群:HHT作为一个新颖的自适应信号处理方法,在语音信号处理,机器健康监测,生物医学工程,建筑,金融数据分析领域中有着广泛的应用,如在医院可用于分析心律不整和血压变化,公路管理局可用其测量公路、桥梁的安全,海军可用其探测潜艇,地震工程可用其分析地震波,汽车行业可用其对柴油机气门漏气故障诊断。由于算法比较新,现阶段市场上还没有基于HHT的信号处理芯片。本设计主要针对市场上HHT信号处理芯片的缺口,开阔一个新的芯片品种同时推广HHT在工程领域的应用。随着HHT在各个领域中的广泛应用,对于HHT芯片的需求量必然迅速增加。由于HHT算法的复杂性和高运算性需要系统运行时间很长,现阶段暂时应用于语音信号机器故障信号分析等低频信号分析,如果能用硬件进行实时处理可以将HHT的应用领域扩展到图像通信等高频信号应用领域。随着HHT的推广,瞬时信号分析将在数字信号处理中起着更广泛的作用。3. 选用本款Altera 器件来进行设计的原因:(1) 接口丰富:① 音频接口:有24bitCD音质的音频CODEC,可以方便的用来输入语音数据,也可以通过line in输入模拟信号,再对信号进行实时处理。② VGA接口:实时显示信号的时间,频率,能量的3D分布图。③ RS232串口:接收需用串口通信的数字信号。可以提供与其它设备简单方便的借口,方便地升级现有的频谱分析设备。④ 网络接口:通过在NiosII处理器上移植uc/os操作系统,从而很方便的实现了其网络功能,既可以作为服务器访问,也可以接入内部局域网进行访问,通过采用以太网方式,实现数据的交互。通过以太网方便用户远程控制并处理和分析各种信号。⑤ LCD接口:显求操作方法提示信息。⑥ 键盘接口:根据算法须要,手动输入参数配置。(2)内存资源丰富:HHT算法需要很大容量的内存空间,而DE1上的512KB SRAM,8MB SDRAM,4MBFlash为数据的暂存提供了充分的空间。如果该空间不够,DE1上还有一个SD扩展槽,可以方便地插入SD卡扩展容量。(3)算法本身的需要:HHT对于非线性非稳定信号虽然自适应性很强,但是算法本身需要巨大的运算量。本设计 主要应用Altera的硬件特性,对算法进行剖析。对于适合顺序运算的部分利用NiosII处理器进行软件实现,对于一些耗时大适合并行运算的部分利用FPGA进行硬件实现。用户自定义指令实现关键算法模块的硬件加速。(4)QuartusII软件对C2H 对算法的支持:利用软件中C2H的功能,可自动地把一些大运算量耗费时间的函数和方程转换成硬件。对算法进行硬件加速不但将大大提高系统的实时处理能力,而且可以免去书写硬件描述语言提高开发周期和效率。(5)可以很容易的实现双核:系统外设较多,HHT算法运算复杂,使用双核有效地提高了系统工作效率。本款atlera器件使我们在代价很低的条件下很容易的实现双核。

(Revision: 7 / 2009-06-15 17:13:55)

2. 功能描述 (Final Project Paper)

该系统利用新颖的HHT算法显示出信号的瞬时频率,可在时域上通过时间-频率-能量的3D分布图像对复杂信号的非平稳变化过程进行分析。本设计从DE2开发板的音频信号采集端读入语音或者其他类型的非线性非稳定信号,经过以太网将采集到的数据传输到PC机端进行HHT的EMD分解处理. EMD处理部分会把信号分解成若干个IMF(本征模态方程), PC机端进行EMD分解时每得到一个IMF就直接将IMF通过以太网发送到NiosII系统中进行下一步HSA(希尔伯特谱分析)。在Nios II系统中,通过硬件加速进行HSA分析。NiosII系统每从PC机端读取到一个IMF之后马上进行HSA分析,这样PC机端在进行EMD分解的同时NiosII也在进行HSA分析实现了PC机端与DE2并行处理。系统经过HSA分析之后既可生成瞬时频率谱。该频谱中横坐标表示时间的变化,纵坐标为频率,频率相对应的颜色的深浅表示在该时刻该频率的能量分分布,颜色越深能量越大。

(Revision: 3 / 2009-09-14 15:27:09)

3. 性能参数 (Final Project Paper)

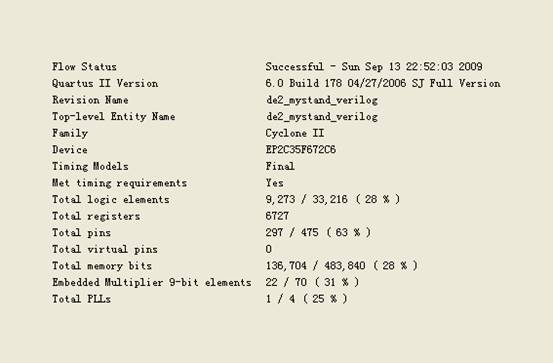

1.系统资源使用情况

2.PC机端EMD分解

关于EMD分解由于巨大的运算量我们最后选择用PC机端实现。调频信号的频率是按着一定规律变化,在做瞬时频率的时候很容易掌握其变化规律.所以我们先对一2048点(512点很难看出频率变化趋势)的调频信号进行了仿真.该信号为

x1= sin(2*pi*t); x2= cos(30*pi*t); y = 15*sin(35*cos(2*pi*t)*pi)+x2;

采样频率为1KHz, 仿真结果如下:(1) 时域调频信号:

(2)变换之后的3D波形图

从以上频谱图中已经可以明显看出该信号瞬时频率的变化趋势。同时对MATLAB和C语言编写的EMD程序进行了运行时间的比较。由于HHT算法的运行时间同时依赖于信号的复杂程度,在此又将一同样2048点的心电信号(采样频率360Hz)引入进行比较。由于运行模式不同,经编写后的C程序效率明显比Matlab中的函数运行速度快,因此在PC端采用了C编写的EMD分解程序。

3. HSA硬件加速模块

HSA(希尔伯特谱分析)通过Hilbert变换实现,这部分在DE2上完成,通过编写相应的自定义外设实现硬件加速。

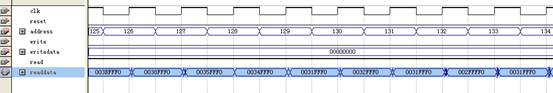

其中Hilbert变换实现主要是由FFT变换以及FFT反变换及一系列数学运算组成,Altera提供了FFT 的IP核,则可通过编写与总线相连的顶层模块,通过调用相应IP核完成FFT自定义外设的设计。FFT模块的变换长度为512点,数据精度选择16位,该自定义外设在Cyclone Ⅱ的EP2C35F484C6上共用逻辑单元4363,占总资源的13%;512点的FFT完成整个运算时间需要512*2+1625=2649个时钟周期,其中收发外部数据需要512*2=1024个时钟周期,FFT IP核计算需要1625个时钟周期。在外部时钟为100MHz时,完成512点的FFT处理时间为26.5μs。仿真图如下图所示。IFFT与FFT通过同一自定义外设实现。

(Revision: 3 / 2009-09-14 15:53:18)

4. 设计结构 (Preliminary Paper)

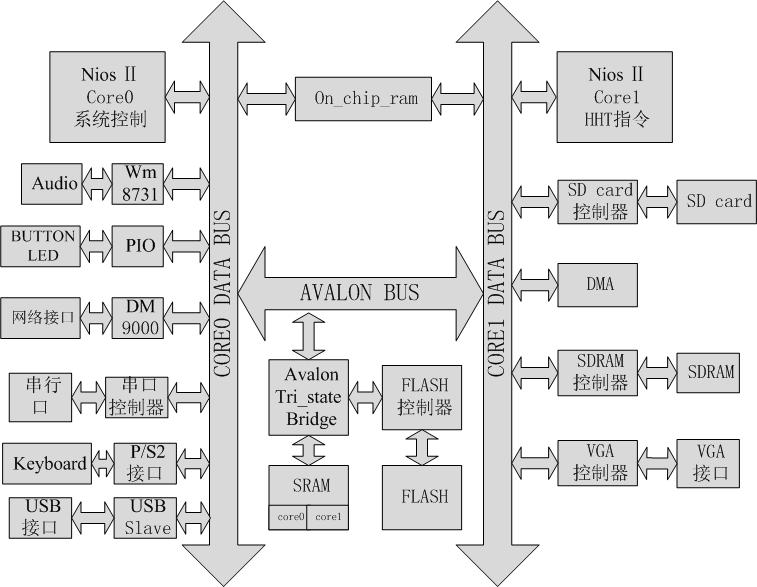

图1.硬件结构图

核0:实现系统总体控制。

核1:主要实现HHT算法。

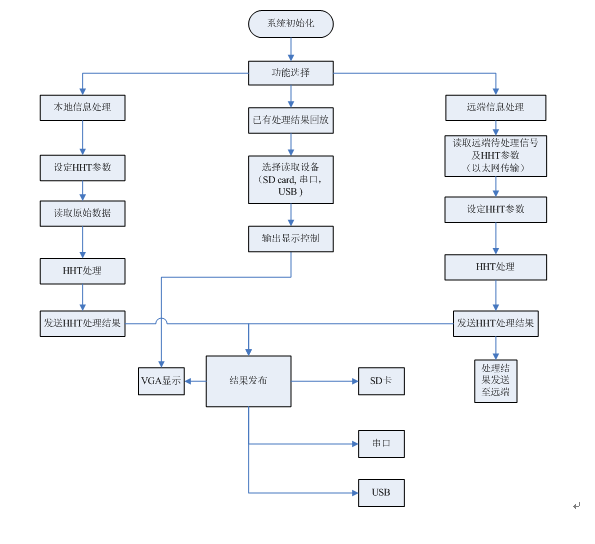

图2.软件流程图

(Revision: 4 / 2009-06-15 16:04:59)

5. 设计方法 (Final Project Paper)

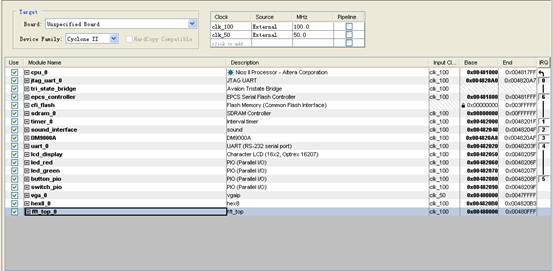

1.sopc架构

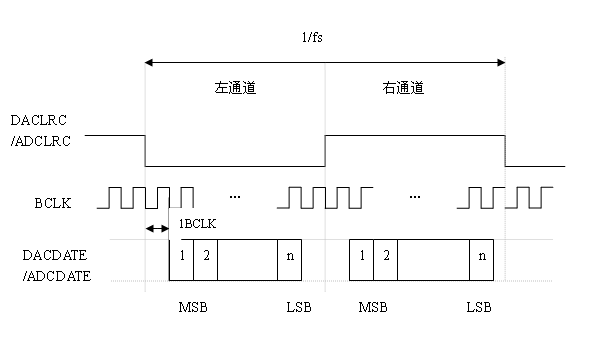

在实际设计中我们根据算法的复杂程度和大赛时间以及NiosII的性能对整个系统进行了重新构架。EMD部分复杂程度过高,部分代码比较适合用硬件实现。但是由于大赛时间有限用硬件对EMD部分进行加速,开发时间不允许所以将EMD部分用PC机实现。根据VGA显示的分辨率和算法本身的要求,EMD对信号每有512个采样点进行处理。AD采样后将数据通过以太网传到PC机端进行EMD分解。在EMD分解过程中每得到一个IMF就马上发给FPGA中的NiosII处理系统进行分析处理,这样在PC机端进行EMD分解的同时NiosII系统也在同时进行HSA分解。(1)信号的采集和VGA显示部分实时信号来源是通过板子上的wm8731采集语音信号得到,它为低功耗立体声音24位音频编/解码芯片。wm8731的音频采样速率为8~96kHz可调;提供2线与3线两种与主控制器的接口方式;支持四种音频数据格式:I2S模式、左对齐模式、右对齐模式和DSP模式。我们将其做成自定义外设,8KHZ采样频率,双通道采样,I2S模式,每采够1024点时,外设申请中断,一帧采样结束,然后将其中任一个通道的数据即512个点通过网络送往主机进行EMD分解。wm8731的音频数据接口时序 I2S模式

wm8731 I2C总路线的时序

音频录放外设

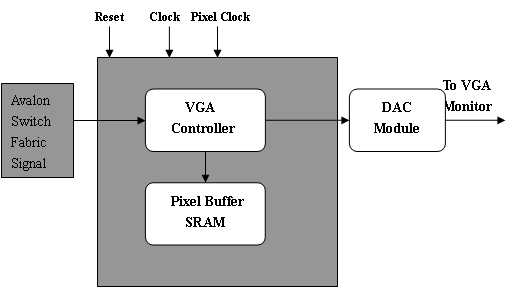

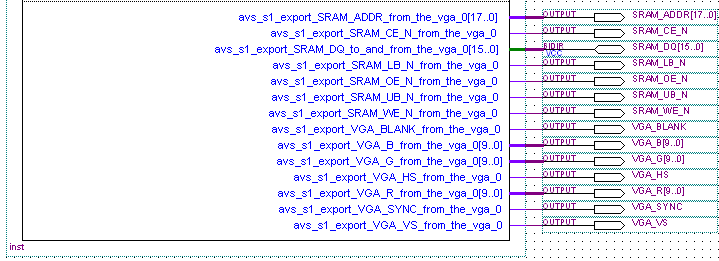

(2) VGA显示模块

我们设计开发了VGA接口。VGA的时序包括水平时序和垂直时序,两者都包含的时序参数有:水平(垂直)同步脉冲、水平(垂直)同步脉冲结束到有效显示数据区开始之间的宽度(后沿)、有效显示区宽度、有效数据显示区结束到水平(垂直)同步脉冲宽度开始之间的宽度(前沿)。水平有效显示区宽度与垂直有效显示区宽度逻辑与的区域为可视区域,其他区域为消隐区。

行/场时序图

VGA控制模块

VGA控制模块

由上图可以看到,SRAM做为图像缓存,它和总线以流传输的方式获得图像数据。因要显示平滑的波形曲线,图像的分辨率要求比较高,我们用的是640*480的分辩率,因sram资源有限,数据位数只能设置成8位,即RGB分别用3,3,2位表示。显示效果:

横坐标代表时间,纵坐标代表频率,颜色显示了其能量,我们用8位数据表示能量,高3位代表红色,中间3位代表绿色,低3位表示蓝色,当数据位全为0时,能量最低,显示黑色,颜色越亮,其能量越高。从图中可能看到,每个时间点上,从纵坐标上可以看到有几个频率和其对应,说明在这个时间点上,有这几种频率成分,每种频率的能量也可以很明显的看到。

而傅利叶变换得到的频谱,每个时间点上的频率是这几种频率的组合,而且每种频率的能量也不能体现出来。

比如一个乐器合奏,每种乐器都发出一种频率的声音,用傅利叶变换得到的频谱图看到的是:每个时刻所有频率的叠加。但是用HHT得到的三维谱图,你可以看到每个时刻都有哪几种频率,可以分析出这个时刻有哪几种乐器在演奏,哪种乐器占得成分多。

2. PC机端EMD分解算法

在程序中有两个循环,一个循环是为了分解IMF,另外一个循环用来判断什么时候停止EMD筛选过程。关于EMD分解主要分为以下几步首先从原始信号x(t)提取出极大值和极小值。然后用三次样条曲线对所有的极大值和极小值进行样条差值得到上下包络线。再取上下包络线的中值m。再用以下公式取出原始信号于中值的差:h(t)=x(t)-m如果h(t)不是一个 IMF, 则h 将被看作是原始信号重新进行分解直到得到一个IMF. 如果i是 IMF, 则存入这个IMF到内存中并同时通过以太网发送到DE2系统中:imf=h ,并且计算剩余量:r=x(t)-imf。把剩余量看作是原始信号x(t)重复以上步骤直到得到另外一个IMF。最后当剩余量或者得到的IMF满足了停止规则就可以停止整个EMD。 3. NiosII系统对HSA部分进行硬件加速FFT算法是由Altera的FFT IP核FFT V2.2.1实现,FFT V2.2.1是一个高性能、参数化快速傅立叶变换(FFT)处理器IP核,对Altera Stratix 以及Cyclone II系列器件进行了设计优化,可以完成变化长度为2的m次方(6≤m≤14)的基-2/4按频率抽取(DIF)的复数FFT算法,IP核使用模块浮点结构可在数据处理过程中保持最大数据动态范围,以获得最大信噪比SNR与最少逻辑需求之间的平衡。此处FFT V2.2.1相关参数设置为:变换长度选择512点,数据精度选择16位,I/O数据流选择Burst形式,复数乘法结构(Structure)由3个乘法器、5个加法器完成。下图给出了FFT IP核的外部端口,I/O接口协议采用Atlantic接口,输入接口为主设备汇端(Master Sink),输出接口为主设备源端(Master Source)。

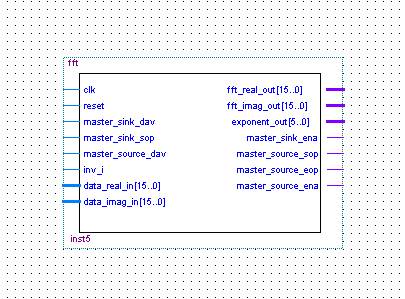

3. NiosII系统对HSA部分进行硬件加速FFT算法是由Altera的FFT IP核FFT V2.2.1实现,FFT V2.2.1是一个高性能、参数化快速傅立叶变换(FFT)处理器IP核,对Altera Stratix 以及Cyclone II系列器件进行了设计优化,可以完成变化长度为2的m次方(6≤m≤14)的基-2/4按频率抽取(DIF)的复数FFT算法,IP核使用模块浮点结构可在数据处理过程中保持最大数据动态范围,以获得最大信噪比SNR与最少逻辑需求之间的平衡。此处FFT V2.2.1相关参数设置为:变换长度选择512点,数据精度选择16位,I/O数据流选择Burst形式,复数乘法结构(Structure)由3个乘法器、5个加法器完成。下图给出了FFT IP核的外部端口,I/O接口协议采用Atlantic接口,输入接口为主设备汇端(Master Sink),输出接口为主设备源端(Master Source)。

fft模块

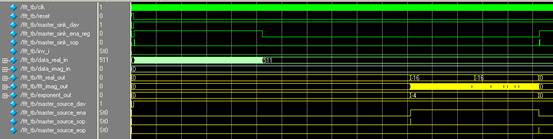

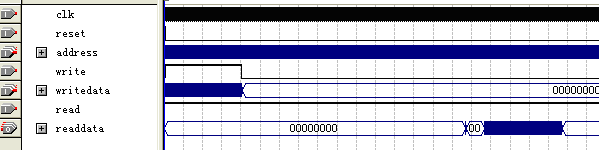

FFT IP核在Modelsim

环境下的仿真结果

通过编写输入输出控制程序,调用FFT IP核实现FFT的自定义外设。在Nios系统中用户自定制外设必须与指定的端口类型匹配,对于FFT来说,其输入和输出都是实部和虚部为16位的复数,正好可以用一个32位的值来表示 这样fft_top.v程序的端口(port)可以按如下方法设置:module fft_top ( // Bus protocol ports, do not add or delete.clk,reset,write,read,address,writedata,readdata);input clk;input reset;input write;

input read;input [9:0] address;input [31:0] writedata;output [31:0] readdata;其中writadata的高16位输入复数的虚部,低16位输入复数的实部,输出端口readdata同writadata。data_real_in_m[address - 1] <= writedata[15:0];data_imag_in_m[address - 1] <= writedata[31:16];当调用该自定义外设时第一个输入的数据决定外设是做FFT还是IFFT,0代表FFT,1代表IFFT。输入输出使用同一FIFO减少系统资源消耗,通过验证自定义外设与IP核运行结果相同。

(Draft / 2009-09-14 17:02:13)

6. 设计特点 (Preliminary Paper)

1、uc/OS实时操作系统成为本系统各功能模块有序运作的一个重要因 素,引入操作系统,直接使用嵌入到NiosII下的操作系统,负责各个功能模块的任务调度,以此来稳定与提高整个系统的性能,简化我们系统的设计。2、用户自定义外设实现关键算法模块的硬件加速,集成到基于FPGA的NiosII子系统中。3、便于产品的升级与开发,本作品的升级与开发空间大,HHT算法仍在不断的完善,依托与NIOSII处理器灵活的可编程性,加上FPGA的可编程性,可以在很短的时间内就可以开发出新的产品。4、本系统的显示部分采用VGA显示,通过在NiosII软核处理器中加入VGA控制器,尽可能的利用开发板资源实现频率时间能量的显示。(Revision: 4 / 2009-09-14 17:05:28)

7. 总结 (Final Project Paper)

此次设计利用SOPC完成了系统的设计,通过AD采集信号PC机和DE2并行处理信息并在VGA上显示了瞬时频率的波形.由于DE1资源有限,最终我们选择的DE2开发平台。在HHT的HAS部分算法中我们加入了自定义外,利用硬件IP核和查找表的方法对算法进行了硬件加速。同时利用Audio in对信号进行采集,并把3D界面的损失频率谱在VGA上成功显示。在PC机端利用C语言自行开发了EMD处理程序,并通过DM9000A芯片与DE2进行数据交换。大赛时间有限,我们只完成了部分功能。如果有跟多的时间和更高级的平台我们会把这个系统做的更好。大赛使我们深刻理解了SOPC的设计理念,使我们可以根据自己的需要定制系统,正是激发学生创新之处。本设计充分发挥了FPGA高度集成的优点。最后感谢Altera公司为我们提供了非常好的理论与实现相结合的实践机会,通过大赛,使我们的理论学习得到了很好的实践。

(Draft / 2009-09-14 17:11:19)

.bmp)