整體架構

本研究的目的即在於開發一套能夠利用閃光誘發腦波電位 (Visual Evoked Potential, VEP) 作為控制訊號的高傳輸率腦波人機介面 (Brain Computer Interface,

BCI),做為啟動外部設備或者表達使用者意圖的管道。

世界上許多研究團隊試圖發展不需要依賴肌肉和神經的溝通技術,而其中一種可行的方法是使用腦電訊號,作為使用者傳達意念的控制訊號,這樣的技術就被稱作腦波人機介面技術。而一個好的腦波人機介面必須先包含下列要件:

(1) 良好的實驗設計以誘發穩定的腦波訊號。

(2) 有效的訊號處理程序以萃取正確的腦波訊號。

(3) 適當的輸出控制裝置以增加系統實用性及完整性。

本研究團隊就是秉持以上幾點要件,開發一套具有商品化特性的腦波人機介面,最終目的可望造福社會,幫助到有需要的少數弱勢族群。以下就針對大腦人機介面系統以及視覺誘發電位兩大主題作更進一步的討論。

1. 大腦人機介面系統 (BCI)

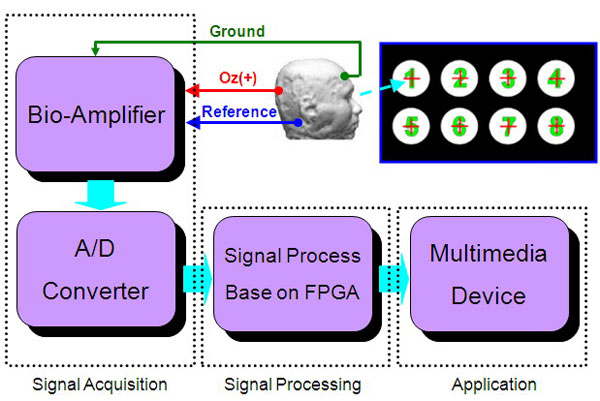

所謂 BCI 是一個連結大腦與外界設備的裝置,BCI 能夠接收到大腦所下達的指令,也能夠將外部訊號直接的送到大腦上。目前 BCI 主要可分為非侵入式和侵入式兩種,此兩種方法互有優缺點,簡單來說,非侵入式電極所獲得之訊號失真程度比侵入式嚴重,但危險性相對較低。因為考慮到危險性,所以大部分研究還是選擇非侵入式的方式,本研究亦是如此。圖一為本系統完整的架構流程圖。

|

圖一、整體系統架構圖

|

2. 視覺誘發電位

視覺誘發電位是指當人眼受到外界視覺刺激,在大腦視覺區中所產生對應的生理訊號。外來的視覺刺激在大腦裡所誘發的訊號,可在頭皮上或是腦皮層上量測到訊號,一般會選擇使用腦電記錄器 (Electroencephalograph, EEG) 來獲得並紀錄誘發的電位,但一般 EEG 價格相當昂貴,經本研究團隊謹慎評估,決定自行設計類比訊號放大系統,取代 EEG,將大幅降低研究成本的投入。

VEP 又可再細分為暫態視覺誘發電位 (Flash Visual Evoked Potential, FVEP) 與穩態視覺誘發電位 (Steady-state Visual Evoked Potential,

SSVEP),最主要差異在於閃光編碼方式以及訊號處理的不同。FVEP 採用隨機編碼方式產生閃光序列,且訊號處理只擷取閃爍光源由暗到亮 (Flash Onset) 的一瞬間所誘發的訊號。相較於 FVEP,SSVEP 擷取一個固定時間長度,經由快速傅立葉轉換 (Fast Fourier Transform, FFT)做頻率偵測,然而本研究團隊利用 SSVEP 的閃光具有單頻特性,僅處理單點的 FFT 轉換,縮短系統處理時間,達到即時 (Real-Time) 性。

|

| |

| 數位電路

|

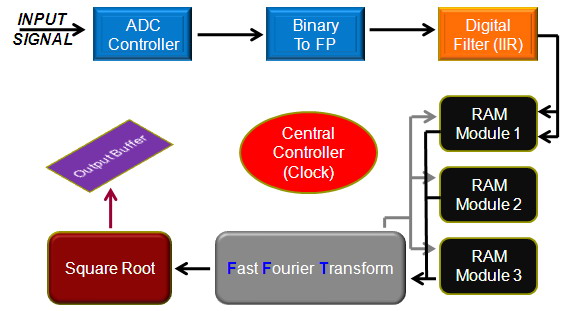

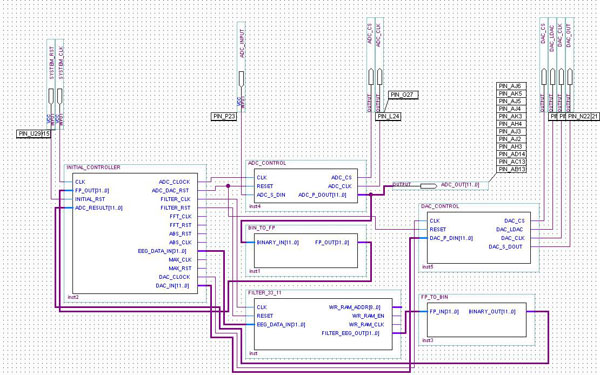

| 本系統於 Filed Programmable Gate Array (FPGA) 所研發之腦電訊號處理模塊其組要架構層級可為 「A/D Converter Controller」、「Binary translate to Floating point」、「Digital Filter:Infinite Impulse Response Filter, IIR Filter」、「Ram Module」、「Fast Fourier Transform: Decimation-In-Frequency, DIF FFT」、「CentralController」、「Floating

Point Arithmetic」。其數位系統架構工作流程如圖一所示。 |

|

| 圖一、數位系統架構流程圖

|

| |

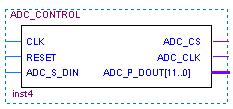

1.ADC Controller:

作為與外部類比電路溝通之橋樑,主司控制外部 12-Bits A/D Converter Chip,並透過 Altera DE1 之 GPIO 進行接收由 12-Bits A/D Converter Chip 量化之腦電訊號,其數學運算格式為二進制 (Binary)。圖二為本系統中以 FPGA 實現之 ADC Controller 硬體電路圖。 |

圖二、ADC

Controller 硬體電路圖 |

| |

2. Binary Translate to Floating Point Arithmetic:

腦電訊號強度十分微弱,因此經由外部類比電路放大、濾波處理後,其干擾雜訊依然存在,再經由 12-Bits A/D Converter Chip 量化後,其數值演算須以浮點運算 (Floating Point Arithmetic) 才能足以表達訊號的精確度。圖三為本系統中以 FPGA 實現之 Binary Translate to Floating Point Arithmetic 硬體電路圖。 |

![]()

圖三、Binary

Translate to Floating Point Arithmetic 硬體電路圖 |

| |

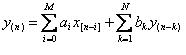

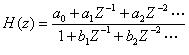

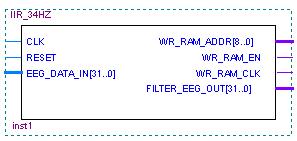

3. Digital Filter- Infinite Impulse Response Filter, IIR:

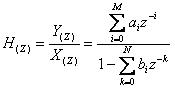

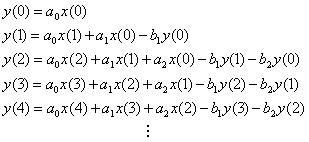

無限脈衝響應濾波器 (IIR Filter) 與有限脈衝響應濾波器(Finite Impulse Response Filter, FIR) 特徵上的差別就是在其差分方程式中IIR 與輸入、輸出有關,而FIR只與輸入有關,由於本系統欲將數位濾波器採硬體實現方式於 Filed Programmable Gate Array (FPGA) 中,因此其運算速度可保證比一般系統單晶片或嵌入式系統等快速許多,再者,本系統並不需求線性相位的性質,因此本團隊經商確考量後決定以 IIR Filter 作為實現於本系統 FPGA 中數位濾波器的角色。 式(1) 為無限脈衝響應濾波器 (IIR Filter) 的差分方程式,而式(2) 為其在 Z domain 下的轉移函式,清楚的寫出輸入與輸出的關係。將 (1)、式(2) 展開可得式(3)、式(4)。 |

(1) (1)

(2) (2)

(3)

(3)

(4) (4)

|

| |

由式(3)、式(4)可看出其在Z domain 轉移函式下的係數即與在 T domain 下的係數相同,其中式(4) 分子的部分則表示了式(3) 輸入的部分,式(4) 分母的部分則代表了式(3) 輸出的部分, 則表示為前一筆資料,於 FPGA 則是延遲至下一次的運算。

圖五為IIR-34Hz的Band-Pass-Filter 其頻帶範圍為[33 35]Hz,可透過軟體工具 Matlab 計算出其所需求之 IIR Filter 轉移函式的係數。IIR濾波器的設計流程為圖四所示,其流程包括有

1. 準備欲經濾波的資料 2. 準備濾波器之係數 3. 進行浮點乘法運算 4. 進行浮點加、減法運算 5. 將輸入與輸出移至延遲暫存器 |

| |

圖四、數位濾波器設計流程

|

圖五、IIR

FILTER 硬體電路圖

|

| |

圖六、IIR

Filter 實測硬體架構 |

| |

圖五為本系統中以 FPGA 實現之 IIR Filter 硬體電路圖,圖六為實測硬體架構當中包括了「Central Controller」、「Floating Point Arithmetic」、「A/D Converter Controller」、「Binary translate to Floating point」、「Digital Filter:Infinite Impulse Response Filter, IIR Filter」、「Floating point translate to Binary」、「D/A Converter Controller」 硬體電路。

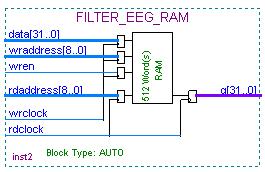

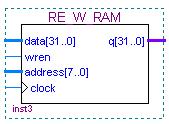

4. RAM Module:

濾波後的資料,由於後續需處理512點快速傅立葉變換(Fast Fourier Transform, FFT),因此需要把濾波後的資料暫時儲存於記憶體中,因此本系統所設計之記憶體模組是採用 Altera Mega-Function Lpm-Ram-dp儲存濾波後的資料如圖七所示,而後續的 Fast Fourier Transform (FFT) 演算所需求之蝶形因子則使用 Altera Mega-Function Lpm-Ram-dq 儲存之,作為查表法 (Look Up Table, LUT) 的運用,如圖八所示。 |

| |

圖七、Altera

Mega-Function Lpm-Ram-dp硬體電路 |

| |

圖八、Altera

Mega-Function Lpm-Ram-dq 硬體電路 |

| |

5. Fast Fourier Transform, FFT

離散傅立葉轉換 (Discrete Fourier Transform, DFT) 在數位訊號處理與分析中是極為重要的角色,可以將 T domain 的離散資料轉換至 Frequency-domain形式的重要演算法。式(5) 為離散傅立葉的表示式。

(5)

式(5) 中 稱之為蝶形因子 (Twiddle Factor),考慮式(5)即可清楚知道,在執行此演算法時需要大量的複數乘法與複數加減法,如256 點之DFT 其運算量為 個複數乘法與 個複數加減法,因此採用 DFT 作為訊號處理的角色則使系統達到Real-Time是不可能的。 快速傅立葉轉換 (Fast Fourier Transform, FFT) 能降低運算量是考量到蝶形因子的特性,式(6) 與式(7) 為蝶形因子的周期性與對稱性質,FFT 即利用其性質使之運算量大為降低。

(6) (7)

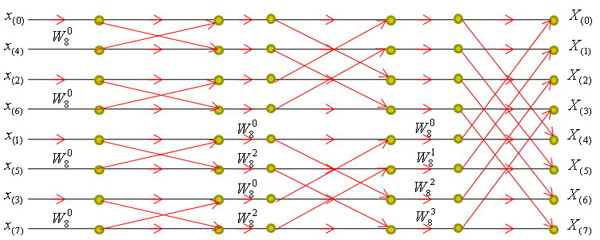

快速傅立葉轉換 (Fast Fourier Transform, FFT),有一其性質即「位元反轉」,其意思為若輸入的時域離散資料為按照順序排列,即 、 … 則會出現輸出為倒序的現象。舉例來說,若資料共為8筆,其分別為 ={n |n=「000」、「001」…「111」},則其輸出 ={m |m=「000」、「100」、「010」、「110」、「001」、「101」、「011」、「111」},如此在運算過後還需要有足夠的記憶容量來儲存在頻域下的輸出再導正其次序,徒增麻煩。因此在 FFT 演算法中的兩種模式為「頻域抽取 (Decimation-In-Frequency, DIF FFT)」、「時域抽取 (Decimation-In-Time, DIT FFT)」,其中 DIT FFT 即是輸入為順序排列輸出為倒序排列,而 DIF FFT 則是輸入為倒序排列輸出為順序排列,因此本系統於 FPGA 中所實現之 FFT 為「頻域抽取之快速傅立葉轉換 (Decimation-In-Frequency, DIF FFT)」。 頻域抽取之快速傅立葉轉換 (Decimation-In-Frequency, DIF FFT) 其推導如下所式。式(8) 為離散傅立葉表示式,將輸入資料分成積項序列(Odd-Term) 2r+1、偶項序列(Even-Term) 2r,可表式為式(9),並稍微整理可得式(10)。

(8) (9)

(10)

再將偶項序列定義為 、積項序列定義為 可表式於式(11) 與式(12),其中 k={k |k= 0、1、2、3… N/2} 。

(11) (12)

因此其離散傅立葉演算法之差分方程式可改寫為式(13) 與式(14)

(13) (14)

依照此模式進行推導可以導處各層級的關係,依照各層關係即可畫出蝴蝶型訊號流程圖,最後式(15) 為8筆資料的8點 DIF FFT 的表示式。

(14) |

| 其圖九為參考式(15)

所會出之

8 point DIF FFT 之訊號流程圖

|

圖九、8-point

DIF FFT 訊號流程圖

|

| |

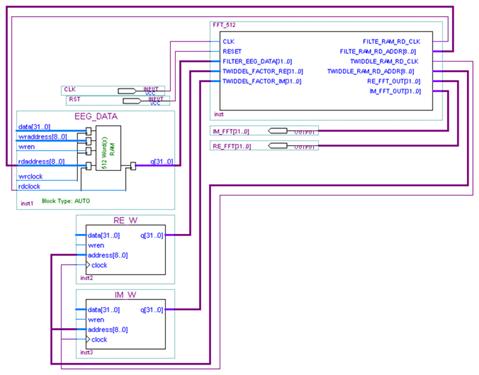

| 圖十本系統 FPGA 中所設計之 DIF FFT架構為512 點 DIF FFT 的硬體電路,其主要滿足於系統的取樣頻率為 1kHz,可於時間範圍內運算完成,而演算法中所需求的蝶形因子之數據主要是採用查表法 (Look Up Table, LUT) 的建立方式,先將數據經由軟體工具 Matlab 計算過後再採用 Altera 之IP core lpm-ram -dq 儲存,以供再進行 FFT 演算讀取使用之。其中本系統在類比濾波放大器後訊號經過 A/D Converter 量化轉換,再透過 Altera DE1 之 GPIO 作為輸入媒介,在經由 FPGA 內所設計開發之 IIR 數位濾波器濾波後將數值儲存於 Altera 之 IP core lpm-ram -dp內,再經由 DIF FFT 提取出作為訊號處理分析之外,其頻域上之數值亦表示為其某頻率之能量強度,亦可當作為辨識的依據。 |

| |

圖十、512-Point

DIF FFT硬體電路 |

| |

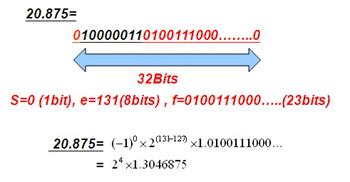

6. Floating Point Arithmetic

式(16) 是依據 IEEE754 Standard 所提供之 32-Bits 浮點運算 (Floating Point Arithmetic) 的標準格式,其中 s為符號位元、e 為偏差指數、f為尾數,圖十一為浮點格式的舉例。 (16) |

圖十一、浮點運算格式範例 |

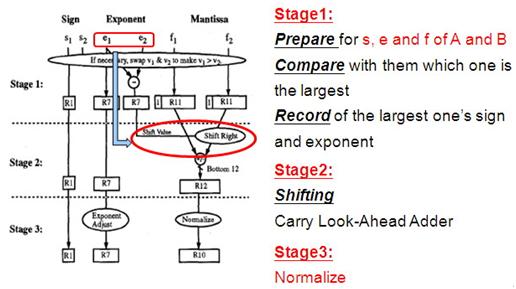

| 圖十二為浮點加法器 (Floating Point Adder)硬體電路圖,圖13為設計浮點運算加法器的設計流程。設計浮點運算加法器是採用前瞻進位加法器作為浮點運算加法器的基底,目的為使降低加法器的輸出延遲。圖13為浮點運算減法器的硬體電路圖,其設計理念大致與加法器相同,僅其基底改為減法器電路。 |

圖十二、浮點運算加法器硬體電路圖 |

| |

圖13

、浮點加法器設計流程圖

|

| |

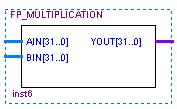

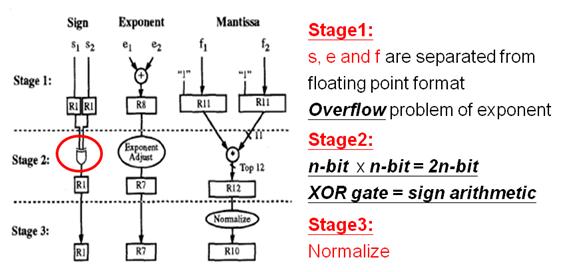

| 圖十四為浮點乘法器的硬體電路圖,圖十五為浮點乘法器的設計流程,其在設計上容易了解,僅需注意「符號位元」、「偏差指數」的運算,「尾數」乘法的部分是採用 Altera FPGA 的內建乘法器來建構而成。 |

| |

圖十四、浮點乘法器硬體電路 |

| |

圖十五、浮點乘法器設計流程圖 |

| |

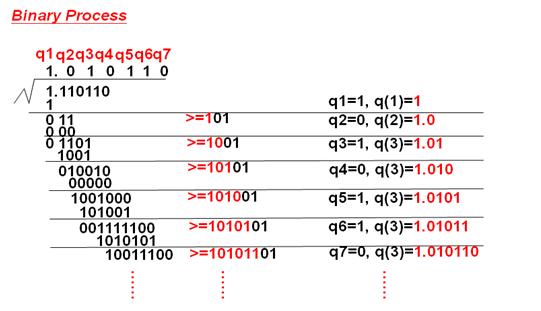

| 圖十六為浮點平方根

(Square Root)的硬體電路,圖十七為為在設計浮點平方根的設計示意圖,每一級的判斷都由上一級的判斷結果加上「01」作為判斷的標準;依照 IEEE

754 32-Bits 浮點運算的標準格式,本系統所設計的

32-Bits 浮點平方根停止條件是硬體電路會持續做到尾數23位元都求得即停止。

|

| |

圖十六、浮點平方根硬體電路

|

| |

圖十七、浮點平方根設計示意

|

| |

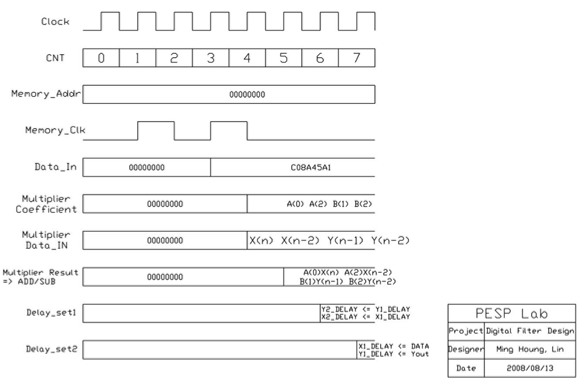

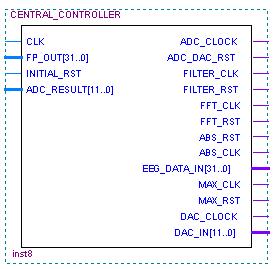

7. Central Controller

由於本系統於腦電波訊號處理取樣的部分,其取樣頻率為1kHz即代表一秒鐘內可取得1000筆離散腦電訊號資料,一筆腦電訊號資料運算時間為 1m s,因此 Central Controller 所扮演的角色是用於決定整個系統架構各元件 「A/D Converter Controller」、「Binary translate to Floating point」、「Digital Filter:Infinite Impulse Response Filter, IIR Filter」、「Ram Module」、「Fast Fourier Transform: Decimation-In-Frequency, DIF FFT」 所佔用的運算時間,也是個元件之間溝通的橋梁。圖十八為 Central Controller 的硬體架構圖, |

圖十八、Central

Controller 硬體架構圖

|

| |

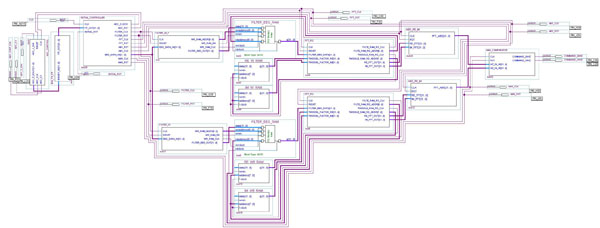

| 圖十九為本系統於處理腦電訊號的硬體電路,經接收量化數據、演算格式轉換、數位濾波、記憶體配置、傅立葉變換、最大值比較器、浮點運算的硬體電路,其中傅立葉變換為計算某頻率之能量強度,因此僅需對所需求的辨識頻率進行單點傅立葉變換後,再經由絕對值運算、最大值比較器,即可辨識出受測者目前是在注視哪一個閃光面板的頻率。由於傅立葉變換部分僅須演算出一點,其他頻率的辨識採並行處理,因此可加快系統辨識的執行速度。 |

| |

圖十九、腦電訊號辨識數位硬體電路

|

6. 設計特點 (Preliminary Paper) |

本作品的特點為使用硬體 FPGA(Altera DE-1)為核心,設計出新一代的大腦人機介面(Brain Computer Interface, BCI)。設計出只需使用者的腦電波(Electroencephalogram, EEG)訊號,即可操控周遭機器。此作品可以應用於漸凍人/四肢癱瘓病患或其它特殊場合等需求。例如漸凍人病患雖然無法藉由四肢來操控周邊電器裝置如電視與空調,但是只要病患的意識是清楚的,就可以透過我們的作品來將其想法或意念傳達出來,進而控制周遭電器裝置。如此除了可以減輕看護或病患家屬的負擔,還可以增加病患的生活自主性與提升其自尊心與生活品質。

由於腦電波訊號辨識演算法含有大量的數學運算,使用硬體 FPGA 實現腦電波訊號處理演算法可以有效地加速腦波訊號辨識速度外,並且可以容易的將辨識結果(命令)透過 FPGA 硬體矽智財(Intellectual Property, IP)來加速系統多媒體周邊環境開發。實現以腦電波訊號控制多媒體系統如撥放音樂、電影或上網等。

(1) 通常腦電波訊號的偵測與分析需要耗費相當長的時間,這會提高使用上不方便性以及無謂的等待時間,為增加使用上的方便性以及商品化的可能性,將訊號處理演算法實現於 FPGA ,提高頻率偵測的速度,控制命令下達更快速,在使用上可以避免耗費無謂的等待時間。

(2) 為使設計者專心於核心演算法的開發,周邊控制器可藉由 Altera 官方之 IP 或其它第三方提供之 IP 加以整合,實現規模較大的系統。

(3) 對於視覺誘發面板的設計,原設計是由它類處理器產生不同頻率訊號於 LED 上,做為刺激視覺誘發電位之閃爍光源,透過 Altera DE1 即可將此設計移植於本系統,更可於 Altera DE1 的顯示面板上設計更精美之閃爍光源面板,使得本系統更趨向於商品化。

(4) 系統原為腦電波訊號放大電路、腦電波訊號分析/辨識演算法使用 FPGA 實現與視覺誘發面板使用它類處理器,藉由 Altera DE1 則可將後述兩項同時實現於此板中,使得開發成本大為降低;此外,可於 Altera DE1 中設計當下流行之趨多媒體系統,藉由腦波訊號控制功能選項如:撥放音樂、電影、上網等等。 |