1. 設計介紹

本作品的設計目的為提供一般提琴樂器練習時的輔助工具,此輔助工具可應用於協助提升個人或團體提琴演奏的品質。簡單的說就是藉此工具提升提琴演奏者對於手指按壓於琴弦上正確位置的精準度,讓提琴能發出正確音準。最後我們期望能做出成本低廉、操作簡易且實用的產品。

DE1發展平台是由Altera公司所設計生產的可程式化硬體平台,此開發平台的相關周邊設計是依據目前最普遍的多媒體產品規格來配置。而且DE1有許多特性都相當適合處理聲音訊號,像是DE1包含了8Mbyte SDRAM、4Mbyte Flash Memory、Audio CODEC with line-in等,最重要的是DE1配有FPGA的優勢,讓DE1擁有高性能、低價位、具有可程式化的特點,使我們能夠完成及時的訊號處理。

至於輸出端,我們藉由網路連結電腦,在電腦顯示每次的練習結果,簡單明瞭的界面讓使用者輕易了解。透過統計會顯示分數較低的地方,讓練習者知道自己常在何處出錯,可以針對常出錯的地方進行調整;透過整體分數的分析,練習者可以知道每天是否有持續進步。藉由本作品會讓人覺得練琴不再只是無聊的練習,練習者可以馬上知道錯誤的地方而進行修正,若透過本作品而知道自己有持續進步時也會增加自信心。

2. 功能描述

本作品在練習者演奏提琴時,會紀錄練習者在琴弦上按壓後所發出的音頻資料,並利用此資料與預先建立好理想的音頻進行比對,比對結果代表練習者在琴弦上按壓的位置與理想位置的差距,分數越低表示差距越大,最後,將此比對之後的結果儲存於SD card。本作品會累計每次練習資料,給予練習者一個統計資訊,提供練習常出錯的地方及整體分數,以協助提升練習者在琴弦上按壓位置的正確性。本作品設計包含下列三個主要設計區塊:

Ø 濾波器

由於雜訊干擾總是無所不再,無論在何處自然界是不可能完全靜音,而麥克風在接收及傳輸也無法避免雜訊的干擾。然而雜訊干擾通常會降低辨識的準確度,因此需要做一些處理來降低雜訊的影響,繼而提升辨識度,我們將細節關鍵分別敘述如下:

- 由於雜訊的干擾,會影響結果的精確度,若能確定樂器所發出的頻帶,透過濾波器加以濾除不考慮的頻帶,藉此減少雜訊干擾來得到較好的結果。

- 首先利用LPF約略限制頻率太高的訊號,主要針對樂器所不可能產生的高頻訊號。我們視這些過於高頻的訊號為雜訊,透過LPF加以濾除。

- 接著再經由BPF準確的限制所需的頻帶,主要針對不同樂器所產生的頻帶也不同的特性,我們將對不同樂器設計各自的BPF。

Ø 高效率的FFT轉換

在這次所要呈現的演算法中,離散傅利葉轉換(DFT) 將信號由時域轉換至頻域,在本作品被用來判斷音階的依據。由於演算法對於頻域解析度的要求,而且為了處理語音信號,取樣率只能低至8ksps,因此需要提高DFT的轉換長度;但是隨著轉換長度的增加,會提高運算在時間上的複雜度。因此,我們設計一個高效率的FFT轉換來達到下列功能:

- 降低記憶體需求

為了節省記憶體使用量與頻寬需求,提出了降低旋轉因子(Twiddle Factor)使用量的演算法。旋轉因子是FFT中用來乘上資料的係數,由於旋轉因子具有對稱性,且正弦與餘弦可互換表示,因此我們將16個旋轉因子縮減成四個,大幅降低原本大量的記憶體需求。

- 精簡運算成本

我們利用DE1上的GPIO擴充兩SDRAM模組,將其設計為同個時間可同時執行讀與寫的動作,雖然需要兩次提取才能得到一筆複數資料;但是將記憶體動作單純化之後,有效的舒緩匯流排的忙碌情形,而大幅提升傳輸效率。

- 突破原平台的效能上限

要計算上萬點的FFT,對這次的專案來說,最大的衝擊就是資源上的問題。在DE1上所使用的FPGA,完全沒有辦法實現16384點ALTRA公司所提供的FFT IP,主要的原因在於這項IP完全使用on-chip的記憶體,雖然有利於高速化運作;但是要延伸轉換長度的話會有資源上的困難。而採用軟體計算FFT這類可以高度平行化的數值計算,沒有辦法展現FPGA的優勢。我們將FFT設計成一個管線化的Radix-4串流(stream)式計算引擎,透過SG-DMA的IP在外部記憶體元件間高速的存取資料,達到資料傳送完成即計算完成的高效率計算。

Ø 音階分析

做音階分析前,必須先切割出音階與音階轉換的位置,如此我們才能比對各個音階是否接近理想狀態,在此我們預計以Hidden Markov Model(HMM)切割音階轉換的位置。知道每個音階所在的位置,就可以利用相對應的FFT訊號得到此範圍的音頻,再拿此音頻與資料庫中理想的音頻比較,便能為練習者打分數。

3. 效能參數

就如同上述所提,本作品是將練習者所演奏的音樂與預先建立好的樂譜進行比對,藉著比對結果告訴練習者在琴弦上按壓的位置是否正確。由於本專案是能即時給予練習者訊息的作品,因此我們對於訊號的處理速度非常講究。本作品在訊號處理上,FFT運算與音頻辨識花費了大部份的運作時間,所以我們必須致力於縮短這兩項主要的訊號處理。

在此先說明我們先前預計要達到的效能,我們統計小提琴練習者變換音階的極限速度,平均一秒的極限約能拉8個音,所以我們的作品最低標準為1秒鐘能夠辨識10個音階。

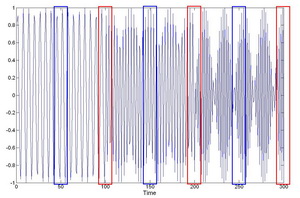

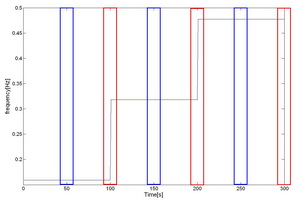

Fig.1 時域訊號示意 圖 Fig.2 時頻域訊號示意圖

Fig. 1 和 Fig. 2分別代表時域訊號與時頻域訊號轉換的示意圖,圖中所示紅色與藍色的框我們稱之為音框,代表其資訊將經過訊號處理得到當時的音階。由Fig. 2可以知一個音框擷取出一段時間區間之訊號,所以音框內部可能不僅只有一個音頻,或許會遇到轉音而含有兩個以上。要有好的辨識結果最好是一個音框只含有一個音頻,若遇到一個音框含有兩個音頻,我們將視此音框正在轉音而不辨識。 觀察Fig. 2可以發現,欲辨識三個音階,至少需要六個音框,才能確定至少有三個音框只含有一個音頻,且這三個音頻分別代表欲辨識的三個音階(也就是Fig. 2的藍框)。由此可以推斷,若要辨識n個音階,至少需要計算2n個音框。以預計的最低標準每秒需辨識10個音階來推斷,就是說本作品每秒至少需要計算20個音框,換句話說辨識每個音框所需的時間不超過50毫秒。 利用本專案所提出的高效率FFT轉換,可以將FFT轉換所需的時間縮短至2毫秒左右,另外音頻辨識所需花費的時間約為16.67毫秒,因此我們辨識一個音框的音頻所需的時間約為18.67毫秒,此數據比最初預計的目標50毫秒少了一半以上。

4. 設計架構

Ø 硬體架構

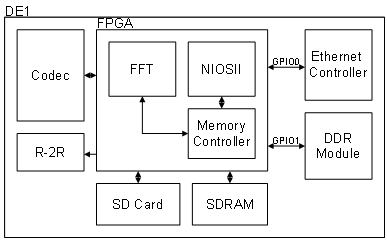

Fig.3 所使用DE1內部之架構圖

- SDRAM:NIOSⅡ的主記憶體。

- SD Card:使用者的紀錄資訊,包括內建的琴譜及練習過程。

- Codec:負責音訊的輸入輸出。

- R-2R:影像輸出介面,方便使用者隨時查看練習情況。

- Ethernet Controller:網路介面。

- DDR Module:FFT主記憶體。

- FPGA:

- FFT:傅利葉轉換硬體模組

- NIOSⅡ:主處理器

- Memory Controller:記憶體控制介面

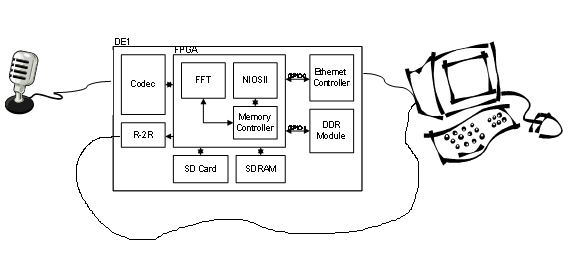

Fig.4 整體架構圖

Ø 硬體架構

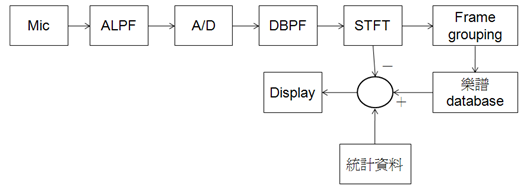

Fig.5 軟體流程圖

Step1. 訊號由麥克風收音後,經由DE1上之CODEC傳進內部之FPGA運算。

Step2. 低通濾波(ALPF)濾除訊號之部分雜訊,而後經由A/D將其由類比轉換為數位訊號;帶通濾波(DBPF)的頻寬範圍則視所使用之樂器而定,使其可應用之幅度更大。

Step3. 利用儲存在DE1上的演算法將訊號進行傅立葉轉換,再與內建正確之資訊對比,所得到之統計資料將顯示於外接螢幕上。

5. 設計方法

Ø 高效能FFT轉換

- 為了要解決記憶體資源的問題,因此設計的第一個重點在於外部記憶體的使用上。DE1板子上的高速同步記憶體只有一顆8MB的SDRAM,已經分配給NIOSII使用,如果把資料的讀寫介面接上去的話,會造成整體fMAX下降及匯流排週期竊取等問題。因此,我們利用DE1上的GPIO擴充兩SDRAM模組,將其設計為同個時間可同時執行讀與寫的動作,雖然需要兩次提取才能得到一筆複數資料;但是將記憶體動作單純化之後,有效的舒緩匯流排的忙碌情形,而大幅提升傳輸效率。

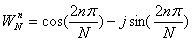

- 接著為了節省記憶體使用量與頻寬需求,提出了降低旋轉因子(Twiddle Factor)使用量的演算法。旋轉因子是FFT中被用來乘上資料的係數,可以寫成以下式子:

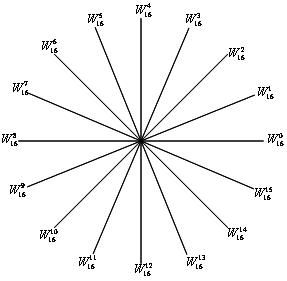

如果用圖形來表示的話,其實就是一個單位圓切成N等分,如Fig.6 :

Fig.6 N=16的旋轉因子

因為數學上的對稱性質,可以將相隔180度的資料加上負號取代,如  = = ,對稱於90度的可以把cosine的部份加上負號,如 ,對稱於90度的可以把cosine的部份加上負號,如 和 和 的關係。最後是對稱於45度,對稱於45度的話,可以將旋轉因子中的cosine與sine互換,以 的關係。最後是對稱於45度,對稱於45度的話,可以將旋轉因子中的cosine與sine互換,以 取代。使用了上述的數學性質之後,其實需要用到的部份幾乎只有第一象限的旋轉因子。 取代。使用了上述的數學性質之後,其實需要用到的部份幾乎只有第一象限的旋轉因子。

- 在本次的專案中,用的是Radix-4的butterfly網路,輸出有四個port,需要乘上

、 、 、 、 和 和 ,因為 ,因為 純粹為1,所以直接寫入硬體中。在此以64點轉換於stage1的情形對演算法做說明,以下是除了 純粹為1,所以直接寫入硬體中。在此以64點轉換於stage1的情形對演算法做說明,以下是除了 所使用到的旋轉因子: 所使用到的旋轉因子:

表2、旋轉因子提取規則表

No. of step |

12 3 4 5 6 7 8 |

|

Engine 1 |

1n |

0 1 2 3 4 5 6 7 |

2n |

0 2 4 6 8 10 12 14 |

3n |

0 3 6 9 12 15 18 21 |

|

Engine 2 |

1n |

1 8 7 6 5 4 3 2 |

2n |

8 9 10 11 12 13 14 15 |

3n |

16 18 20 22 24 26 28 30 |

Step1的時候先個別在兩個運算引擎上執行{0,0,0}和{8,16,24}這兩項旋轉因子的乘法。這個時候除了 會被提取外, 會被提取外, 、 、 和 和 因為位於45度對稱軸上,16點以上的轉換的這組數值都是一樣的,所以係數是內建在硬體中。 因為位於45度對稱軸上,16點以上的轉換的這組數值都是一樣的,所以係數是內建在硬體中。

到了Step2以後,只需要提取Engine1所需的旋轉因子,Engine2用到的旋轉因子會透過數學上的對稱關係從提取給Engine1的旋轉因子中取得,其關係式為:

1n:對稱於45度,將實部與虛部互換。

2n:對稱於90度,將實部做補數轉換。

3n:對稱於135度,將實部與虛部互換,並做補數轉換。

雖然旋轉因子只需要一個單位圓的八分之一就可以透過對稱性質提供給FFT使用;但是這裡為了讓架構精簡,只有把Radix-4 FFT所需要用到四分之三個圓的量壓縮一半到八分之三。然而透過這樣的方式,已經可以將旋轉因子的量減少一半,而且在這次的設計中,FFT所使用的兩個SDRAM模組同一個時間內只有一個可以source八筆複數資料給兩個運算引擎;但是提供旋轉因子的記憶體只需要供應三筆複數資料,頻寬的需求較低,因此選擇與NIOSII共用同一塊SDRAM,由系統動態分配空間。

- 再來,因為Radix-4FFT的特性,資料的讀取並非連續的,DMA並沒有提供這種功能,所以另外做了位址產生器,DMA只要透過這個介面存取記憶體,就可以讀寫所需要的記憶體位址。在寫入的位址產生器中,也加入了可程式的位元反轉遮罩,在執行轉換的最後一個階段的時候,只要設定指令暫存器,產生出來的位址就會透過位元反轉遮罩輸出位元反轉後的位址。目前可設定的有:無反轉、給16點轉換用的至65536共計8組,在控制暫存器中用到4個位元去選擇。

6. 設計特點

本專案設計具有下列幾項特點:

Ø 演算法對預先資訊的需求小,可運用的範疇相對增加。

Ø 將FFT實踐於FPGA上,有助於突破原開發平台上的功能上限。

Ø 管線化的Radix-4串流(stream)式計算引擎,透過SG-DMA的IP在外部記憶體元件間高速的存取資料,使系統的運算極為有效率。

Ø 特殊的旋轉因子表示法,大幅降低記憶體儲存旋轉因子的空間,使系統對於記憶體需求更為精簡。

Altera DE1 多媒體平台協助實現設計特點:

Ø 硬體設計方面:

- 利用SOPC builder 完成各項週邊控制介面整合。

- 利用FPGA設計高效能FFT轉換。

- 進行接腳配置。

- 進行硬體描述語言合成。

- 將所完成之硬體結構燒錄製Flash上,以配置FPGA。

Ø 軟體設計方面:

- 以C 語言完成訊號分離演算法的實作。

- 以C語言完成原始訊號辨識的實作。

Ø 系統整合:

- 以C 語言完成軟體(演算法)及硬體(語音資料傳遞)之間的系統整合。

- 將所完成之軟體系統燒錄製Flash 上。

Ø 系統測試:

7. 總結

藉由這次比賽,我們都盡力將所學的知識應用於實際的情況。大家都體會到理論與實際應用必然有一段差距,真正著手實驗不難發現有許多的理論會假設這些實際上真正的困難點不存在或不考慮,透過這次的比賽我們了解這些理論必須依靠實際應用來證明其價值。在實踐的過程中我們也發現一個作品實在是很難說它是完美的,因為我們常會發掘此作品尚有很多問題。雖然如此,我們依舊盡力發掘問題並改良舊技術甚至產生新技術來解決問題。

|